### **DATA SHEET**

# SKY73101-11: 1930–1990 MHz High Performance VCO/Synthesizer With Integrated Switch

# **Applications**

- 2G, 2.5G, and 3G base station transceivers:

GSM, EDGE, CDMA, WCDMA

- General purpose RF systems

## **Features**

- Frequency operation range: 1930 to 1990 MHz

- Process-tolerant compensation for VCO

- 24-bit  $\Sigma\Delta$  fractional-N synthesizer

- Ultra-fine frequency resolution of 0.001 ppm

- Flexible reference frequency selection

- Three-wire serial interface up to 20 MHz clock frequency

- Integrated PLL supply regulation for spur isolation

- MCM (38-pin, 9 x 12 mm) SMT package (MSL3, 260 °C per JEDEC J-STD-020)

Skyworks Green<sup>™</sup> products are RoHS (Restriction of Hazardous Substances)-compliant, conform to the EIA/EICTA/JEITA Joint Industry Guide (JIG) Level A guidelines, are halogen free according to IEC-61249-2-21, and contain <1,000 ppm antimony trioxide in polymeric materials.

# **Description**

Skyworks SKY73101-11 Voltage-Controlled Oscillator (VCO)/Synthesizer is a fully integrated, high performance signal source for high dynamic range transceivers. The device provides ultra-fine frequency resolution, fast switching speed, and low phase noise performance for 2G, 2.5G, and 3G base station transceivers.

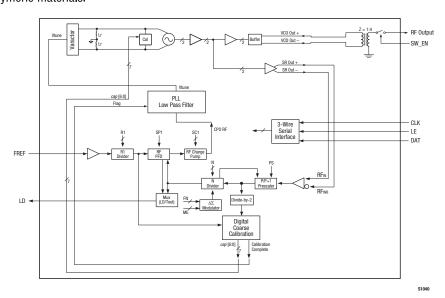

The SKY73101-11 VCO/Synthesizer is a key building block for high-performance radio system designs that require low power and a fine step size. Reference clock generators with an output frequency up to 52 MHz can be used with the SKY73101-11. A functional block diagram is shown in Figure 1. As indicated in this diagram, the reference frequency is divided down by 1, 2, 4, or 8 in the R1 divider, depending on the value of the reference divisor input (R1). Refer to the Reference Input Divider section (page 10) for more information.

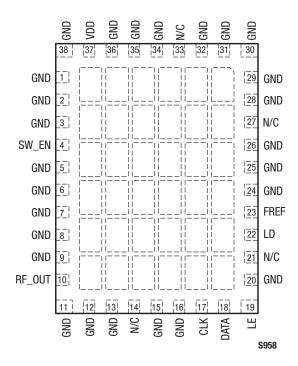

The SKY73101-11 VCO/Synthesizer is provided in a compact, 38-pin Multi-Chip Module (MCM). The device package and pinout are shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

Figure 1. SKY73101-11 Functional Block Diagram

Figure 2. SKY73101-11 Pinout- 38-Pin MCM Package (Top View)

**Table 1. SKY73101-11 Signal Descriptions**

| Pin # | Name   | Description                         | Pin# | Name | Description               |

|-------|--------|-------------------------------------|------|------|---------------------------|

| 1     | GND    | Ground                              | 20   | GND  | Ground                    |

| 2     | GND    | Ground                              | 21   | N/C  | No connection             |

| 3     | GND    | Ground                              | 22   | LD   | Lock detect output        |

| 4     | SW_EN  | Synthesizer RF output switch enable | 23   | FREF | Frequency reference input |

| 5     | GND    | Ground                              | 24   | GND  | Ground                    |

| 6     | GND    | Ground                              | 25   | GND  | Ground                    |

| 7     | GND    | Ground                              | 26   | GND  | Ground                    |

| 8     | GND    | Ground                              | 27   | N/C  | No connection             |

| 9     | GND    | Ground                              | 28   | GND  | Ground                    |

| 10    | RF_OUT | Synthesizer output                  | 29   | GND  | Ground                    |

| 11    | GND    | Ground                              | 30   | GND  | Ground                    |

| 12    | GND    | Ground                              | 31   | GND  | Ground                    |

| 13    | GND    | Ground                              | 32   | GND  | Ground                    |

| 14    | N/C    | No connection                       | 33   | N/C  | No connection             |

| 15    | GND    | Ground                              | 34   | GND  | Ground                    |

| 16    | GND    | Ground                              | 35   | GND  | Ground                    |

| 17    | CLK    | Serial port clock                   | 36   | GND  | Ground                    |

| 18    | DATA   | Serial port data                    | 37   | VDD  | +5 V power supply         |

| 19    | LE     | Serial port latch enable            | 38   | GND  | Ground                    |

# **Technical Description**

The SKY73101-11 is a fractional-N frequency synthesizer using a  $\Sigma\Delta$  modulation technique. The fractional-N implementation provides low in-band noise by having a low division and fast frequency settling time. The device also provides programmable, arbitrary fine frequency resolution. This compensates the frequency synthesizer for crystal frequency drift.

### **Serial I/O Control Interface**

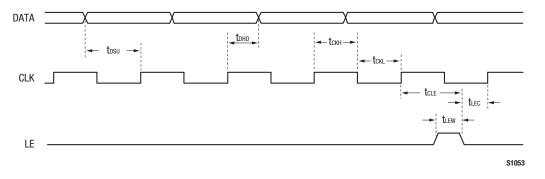

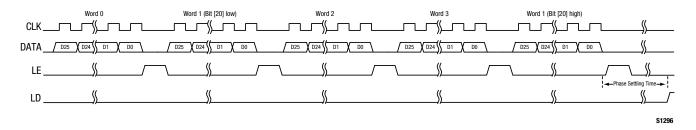

The SKY73101-11 is programmed through a three-wire serial bus control interface using four 26-bit words. The three-wire interface consists of three signals: CLK (pin 17), LE (pin 19), and the bit serial data line DATA (pin 18). The convention is to load data from the most significant bit to the least significant bit (MSB to LSB). A serial data input timing diagram is shown in Figure 3. Preset timing parameter values are provided in Table 2.

Although the SKY73101-11 uses a 5 V DC supply, the internal voltage regulator has a 3.3 V output for the PLL. Therefore, the input DC voltage for the serial interface (CLK, DATA, and LE signals) should be set to 3.3 V or lower.

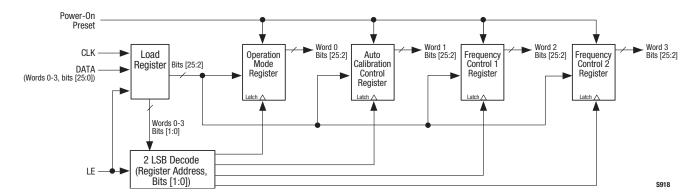

Figure 4 depicts the serial bus, which consists of one 26-bit load register and four separate 24-bit registers. Data is initially clocked into the load register starting with the MSB and ending with the LSB. The LE signal is used to gate the clock to the load register, requiring the LE signal to be brought low before the data load. Data is shifted on the rising edge of CLK.

The two final LSBs are decoded to determine which holding register should latch the data. The falling edge of LE latches the data into the appropriate holding register. This programming sequence must be repeated to fill all four holding registers.

The specific hold register addresses are determined by the wd\_0 and wd\_1 parameters in the load register. These are the two LSBs (bits [1:0]) as shown in Figure 4. Table 3 lists the four hold registers and their respective addresses as determined in the load register.

The contents of each word in the load register are used to program the four hold registers described in Tables 4 through 7.

The dpll\_ctrl parameter (bits [19:2] of Word 1) programs the Digital Phase Locked Loop (DPLL) block. Each of the 18 bits that comprise the dpll\_ctrl parameter map directly to the signal ports on the DPLL block as shown in Table 8 (except for the dpll\_flag\_override and dpll\_flag\_value parameters).

Loading new data into a holding register not associated with the synthesizer frequency programming does not reset or change the synthesizer. The synthesizer should not lose lock before, during, or after a new serial word load that does not change the programmed frequency.

## **VCO Auto-Tuning Loop**

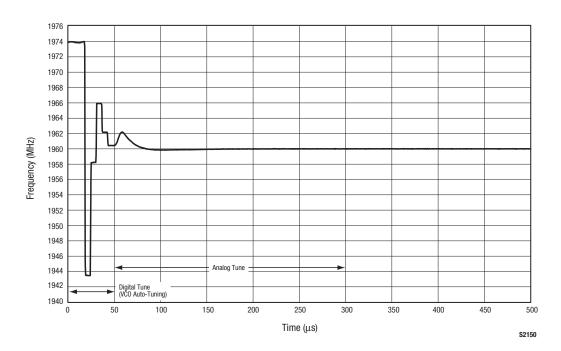

A VCO auto-tuning loop provides the proper 7-bit coarse tuning setting for the VCO switch capacitors in the VCO output. This sets the oscillation frequency as close to target as possible before starting fine analog tuning.

When VCO auto-tuning is enabled, the PLL performs a seven-step successive approximation process to digitally tune the VCO close to the final programmed frequency. Once that is complete, analog tuning is switched in to lock the VCO to the programmed frequency.

The auto-tuning loop is designed to compensate process variation so that the VCO fine tuning range can be reduced to cover temperature variation only. It significantly reduces VCO gain (Kv) which reduces VCO phase noise.

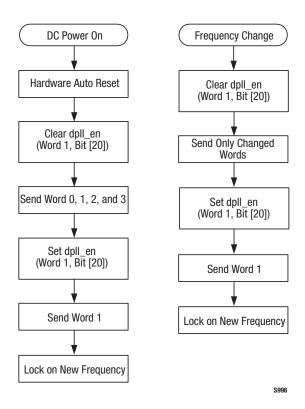

There are two conditions that enable the VCO auto-tuning function: a Power-On-Reset (POR) and a change in frequency. The difference in the program flow under each of these conditions is illustrated in Figure 5. Under either condition, dpll\_en (bit [20] of Word 1) should first be cleared so that a rising edge pulse can be generated. Following this pulse, set dpll\_en to enable VCO auto-tuning.

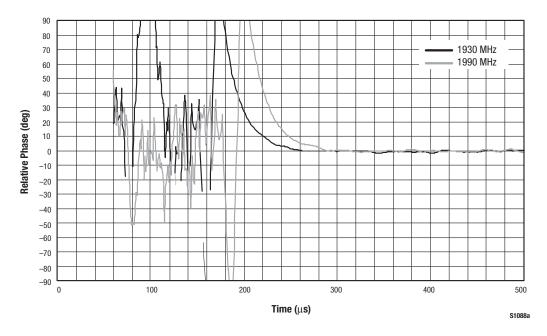

A POR timing diagram is shown in Figure 6. VCO auto-tuning details in the frequency and time domains are shown in Figure 7.

Figure 3. SKY73101-11 Serial Data Input Timing Diagram (MSB First)

**Table 2. CLK, DATA, LE Preset Timing Parameters**

| Parameter                           | Value            |

|-------------------------------------|------------------|

| Input high voltage (ViH)            | 1.6 V            |

| Input low voltage (V <sub>L</sub> ) | 0.3 V            |

| Input current (lois)                | 1 μA (maximum)   |

| Clock frequency                     | 15 MHz (maximum) |

| Clock high (tcкн)                   | 15 ns (minimum)  |

| Clock low (tckl)                    | 15 ns (minimum)  |

| Data set up (tosu)                  | 20 ns (minimum)  |

| Data hold (toho)                    | 10 ns (minimum)  |

| Clock to latch enable (tcle)        | 20 ns (minimum)  |

| Latch enable width (tlew)           | 15 ns (minimum)  |

| Latch enable to clock (tlec)        | 15 ns (minimum)  |

| Word length                         | 26 bits          |

| Number of words                     | 4                |

| Current drain                       | 2 μΑ             |

Figure 4. Serial Bus Block Diagram

Table 3. SKY73101-11 Hold Registers and Addresses

| Hold Register Name       | Hold Register Address (Bin | ary) in Load Register Words |

|--------------------------|----------------------------|-----------------------------|

| noiu negistei Maille     | Bit [1]                    | Bit [0]                     |

| Operation Mode           | 0                          | 0                           |

| Auto Calibration Control | 0                          | 1                           |

| Frequency Control 1      | 1                          | 0                           |

| Frequency Control 2      | 1                          | 1                           |

Table 4. Load Register Word 0 (Programs the Operation Mode Register) (1 of 2)

| Parameter   | Function                                                                                                                                            | State Description                                                                                                                                                                                                                                              | Recommended<br>Operational Value<br>(Binary) |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| wd_0, wd_1  | Address bits [1:0]. Must be set to 00b (see Table 3)                                                                                                |                                                                                                                                                                                                                                                                | 00                                           |

| cp_output   | Charge pump setting [4:2]                                                                                                                           | Bits [4:2]: $0\ 0\ 0 = 200\ \mu\text{A} \\ 0\ 0\ 1 = 400\ \mu\text{A} \\ 0\ 1\ 0 = 600\ \mu\text{A} \\ 0\ 1\ 1 = 800\ \mu\text{A} \\ 1\ 0\ 0 = 1000\ \mu\text{A} \\ 1\ 0\ 1 = 1200\ \mu\text{A} \\ 1\ 1\ 0 = 1400\ \mu\text{A} \\ 1\ 1\ 1 = 1600\ \mu\text{A}$ | Application<br>dependent                     |

| cp_delay    | Charge pump delay [6:5]                                                                                                                             | Bits [6:5]:  0 0 = 2 nsec 0 1 = 4 nsec 1 0 = 7 nsec 1 1 = 9 nsec  NOTE: this device is fixed at 2 nsec.                                                                                                                                                        | 00                                           |

| pd_polar    | Polarity of phase detector [7]                                                                                                                      | Bit [7]:  0 = Negative  1 = Positive  NOTE: this device is fixed at negative polarity.                                                                                                                                                                         | 0                                            |

| cp_tristate | Tri-state selection for the transmit PLL charge pump output [8]                                                                                     | Bit [8]:  0 = Charge pump in normal functional mode  1 = Charge pump disabled/tri-stated                                                                                                                                                                       | 0                                            |

| rsvd        | Reserved [9]                                                                                                                                        | Reserved                                                                                                                                                                                                                                                       | 0                                            |

| sd_sel      | Internal operating voltage control bit for $\Sigma\Delta$ synthesizer [10]  Note: this bit needs to be programmed together with bits [11] and [12]. | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                         | 100                                          |

| nr_sel      | Internal operating voltage control bit for N-counter and R1 divider [11]                                                                            | This bit needs to be programmed together with bits [10] and [12].                                                                                                                                                                                              | -                                            |

|             | See sd_sel parameter (bit [10])                                                                                                                     |                                                                                                                                                                                                                                                                |                                              |

| pll_en      | Internal operating voltage control bit for PLL [12] See sd_sel parameter (bit [10])                                                                 | This bit needs to be programmed together with bits [10] and [11].                                                                                                                                                                                              | -                                            |

| ref_bw_sel  | Reference buffer bandwidth [14:13]                                                                                                                  | Bits [14:13]:<br>0 0 = 20 MHz<br>0 1 = 30 MHz<br>1 0 = 40 MHz<br>1 1 = 50 MHz                                                                                                                                                                                  | 11                                           |

Table 4. Load Register Word 0 (Programs the Operation Mode Register) (2 of 2)

| Parameter    | Function                                         | State Description                                                                                                                                                                 | Recommended<br>Operational Value<br>(Binary)<br>000 |  |

|--------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| test_mux     | Lock detect and diagnostic output select [17:15] | Bits [17:15]:  0 0 0 = Lock detect output 0 0 1 = R-divider output 0 1 0 = N-divider output 0 1 1 = Not used 1 0 0 = Not used 1 0 1 = Not used 1 1 0 = Not used 1 1 1 = DPLL test |                                                     |  |

| rsvd         | Reserved [20:18]                                 | Reserved                                                                                                                                                                          | 000                                                 |  |

| pre_curr_sel | Prescaler current bias [22:21]                   | Bits [22:21]:<br>0 0 = 20 μA<br>0 1 = 22 μA<br>1 0 = 24 μA<br>1 1 = 26 μA                                                                                                         | 00                                                  |  |

| prescale_sel | Prescaler mode select [23]                       | Bit [23]: 0 = Prescaler in 8/9 divide mode 1 = Prescaler in 16/17 divide mode                                                                                                     | Application dependent                               |  |

| rsvd         | Reserved [25:24]                                 | Reserved                                                                                                                                                                          | 00                                                  |  |

## **Table 5. Load Register Word 1 (Programs the Auto Calibration Control Register)**

| Parameter  | Function                                             | State Description                   | Recommended<br>Operational Value<br>(Binary) |

|------------|------------------------------------------------------|-------------------------------------|----------------------------------------------|

| wd_0, wd_1 | Address bits [1:0]. Must be set to 01b (see Table 3) |                                     | 01                                           |

| dpll_ctrl  | DPLL control [19:2]                                  | Refer to Table 8                    | -                                            |

| dpll_en    | Digital PLL enable flag [20]                         | 0 = Disable DPLL<br>1 = Enable DPLL | Refer to Figure 5                            |

| rsvd       | Reserved [25:21]                                     | Reserved                            | 00000                                        |

# Table 6. Load Register Word 2 (Programs the Frequency Control 1 Register) (1 of 2)

| Parameter  | Function                                             | State Description                                       | Recommended<br>Operational Value<br>(Binary) |

|------------|------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|

| wd_0, wd_1 | Address bits [1:0]. Must be set to 10b (see Table 3) |                                                         | 10                                           |

| rdiv       | Reference divider ratio [3:2]                        | Bits [3:2]:<br>0 0 = 8<br>0 1 = 4<br>1 0 = 2<br>1 1 = 1 | Application<br>dependent                     |

| rsvd       | Reserved [5:4]                                       | Reserved                                                | -                                            |

Table 6. Load Register Word 2 (Programs the Frequency Control 1 Register) (2 of 2)

| Parameter     | Function                                                        | State Description                                                                                                                                                                                                                                                                                                                                                      | Recommended<br>Operational Value<br>(Binary) |

|---------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ndiv          | N-divider/prescaler mode for control of M and A counters [15:6] | Bits [15:6]:  Bits [15:10] Bits [9:6]  M bits [5:0] A bits [3:0] = use 16/17 prescaler  M bits [5:0] A bits [2:0] = use 8/9 prescaler  Note: The six MSBs of ndiv denote the M counter value and the four LSBs denote the A counter value. For the 8/9 prescaler mode, the A counter value requires only three bits. Therefore, bit [9] of ndiv is a "don't care" bit. | Application dependent                        |

| rsvd          | Reserved [16]                                                   | Reserved                                                                                                                                                                                                                                                                                                                                                               | 0                                            |

| mod_reset_f   | Modulator reset/fractional mode select [17]                     | Bit [17]:  0 = Modulator is reset or disabled  1 = Modulator is in fractional mode                                                                                                                                                                                                                                                                                     | 1                                            |

| fract_int_sel | Fractional/integer mode select [18]                             | Bit [18]:  0 = Modulator is in integer mode  1 = Modulator is in fractional mode                                                                                                                                                                                                                                                                                       | 1                                            |

| rsvd          | Reserved [19]                                                   | Reserved. This bit should always remain set (logic high).                                                                                                                                                                                                                                                                                                              | 1                                            |

| me            | Modulus extender [23:20]                                        | These four bits need to be programmed together with bits [12:2] of Word 3. Bits [23:20] represent the four LSBs ([3:0]) of the 15-bit modulus extender value (ME [14:0]). Refer to the Synthesizer Programming section of this Data Sheet for further information.                                                                                                     | Application<br>dependent                     |

| rsvd          | Reserved [25:24]                                                | Reserved                                                                                                                                                                                                                                                                                                                                                               | 00                                           |

# Table 7. Load Register Word 3 (Programs the Frequency Control 2 Register)

| Parameter  | Function                                             | State Description                                                                                                                                                                                                                                               | Recommended<br>Operational Value<br>(Binary) |

|------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| wd_0, wd_1 | Address bits [1:0]. Must be set to 11b (see Table 3) |                                                                                                                                                                                                                                                                 | 11                                           |

| me         | Modulus extender [12:2]                              | These 11 bits need to be programmed together with bits [23:20] of Word 2. Bits [12:2] represent the 11 MSBs ([14:4]) of the 15-bit modulus extender value (ME [14:0]). Refer to the Synthesizer Programming section of this Data Sheet for further information. | Application dependent                        |

| fn         | Fractional divisor code [20:13]                      | Bits [20:13] represent the 8-bit fractional divisor code (FN [7:0]).<br>Refer to the Synthesizer Programming section of this Data Sheet for information.                                                                                                        | Application dependent                        |

| rsvd       | Reserved [23:21]                                     | These three bits should always remain cleared (logic low).                                                                                                                                                                                                      | 0                                            |

| rsvd       | Reserved [25:24]                                     | Reserved                                                                                                                                                                                                                                                        | 00                                           |

**Table 8. DPLL Digital Control Bits**

| Serial Port Name   | Load Register Word 1 Bit | Recommended Operating Value (Binary) |

|--------------------|--------------------------|--------------------------------------|

| dpll_clk_dly(0)    | 2                        | 0                                    |

| dpll_clk_dly(1)    | 3                        | 0                                    |

| dpll_temp_comp(0)  | 4                        | 0                                    |

| dpll_temp_comp(1)  | 5                        | 0                                    |

| dpll_temp_comp(2)  | 6                        | 0                                    |

| dpll_temp_comp(3)  | 7                        | 0                                    |

| dpll_temp_comp(4)  | 8                        | 0                                    |

| dpll_temp_comp_en  | 9                        | 0                                    |

| dpll_ext_test(0)   | 10                       | 0                                    |

| dpll_ext_test(1)   | 11                       | 0                                    |

| dpll_ext_test(2)   | 12                       | 0                                    |

| dpll_ext_test(3)   | 13                       | 0                                    |

| dpll_ext_test(4)   | 14                       | 0                                    |

| dpll_ext_test(5)   | 15                       | 0                                    |

| dpll_ext_test(6)   | 16                       | 0                                    |

| dpII_ext_test(7)   | 17                       | 0                                    |

| dpll_flag_override | 18                       | 0                                    |

| dpll_flag_value    | 19                       | 0                                    |

Figure 5. VCO Auto-Tuning Enable Process Flow Due to POR or Frequency Change

**Figure 6. POR Timing Diagram**

Figure 7. VCO Auto-Tuning @ 1960 MHz Frequency Settling

#### **VCO Prescalers**

The VCO prescalers divide the VCO output signal by either 16/17 or 8/9. The  $\Sigma\Delta$  modulator determines whether to divide by 16 or 17 in the 16/17 mode, or whether to divide by 8 or 9 in the 8/9 mode. The 8/9 mode provides the best performance for the SKY73101-11.

#### **N-Counter**

The N-counter consists of two asynchronous ripple counters, a 6-bit M-counter and a 4-bit A-counter. The M-counter determines the counts using the lower division ratio in the prescaler (8 or 16); the A-counter determines the counts using the upper division ratio (9 or 17).

The total N-counter divider ratio for the 8/9 mode is 56 (8  $\times$  7) minimum; for the 16/17 mode, the ratio is 240 (16  $\times$  15) minimum.

By changing the counter setting at each reference clock cycle, the Modulated Fractional Divider (MFD) achieves the desired noise shaping.

### **VCO MFD Block**

The MFD block divides down the prescaler output to the Phase Locked Loop (PLL) reference frequency. A third order cascaded  $\Sigma\Delta$  modulation technique minimizes spurs through randomization of the division ratio.

The MFD block controls the division ratio by dynamically programming the M and A counters in the N-counter.

## **Phase Detector and Charge Pump**

The phase detector and charge pump detect and integrate the phase and frequency errors of the divided down VCO output versus the reference clock. This results in a feedback adjustment of the control voltage for the VCO.

## **Lock Detect**

Lock detection circuitry provides a CMOS logic level indication when the PLL is frequency locked (high when locked). Normally, pin 22 (LD) is used for lock detect output. This pin can also be programmed as the R1 divider output, N-divider output, or DPLL test output. Pin 22 is controlled by Word 0, bits [17:15].

## **Reference Input Divider**

The R-counter (reference input clock divider) consists of three divide-by-two blocks and one multiplexer controlled by the rdiv[3:2] parameter in Word 2. The R1 divider is used to select a divide-by-one, two, four, or divide-by-eight function.

The integral loop filter (see Figure 1) is designed to operate at an internal comparison frequency of approximately 6.5 MHz. The input reference signal must be divided using the rdiv [3:2] bits in Word 2 to closely match this frequency. Further optimization of the loop filter bandwidth may be accomplished using the cp\_output [4:2] bits in Word 0.

## **Reference Buffer Bandwidth**

The two-bit parameter *ref\_bw\_sel* adjusts the operating point of the input buffer to compensate for different reference signal sources. Generally the best setting is 50 MHz, but this could vary depending on the source used.

## **Synthesizer Output Switch**

An on-chip switch is integrated into the SKY73101-11 RF output after the balun and is controlled by the SW\_EN signal (pin 4) as indicated below:

| SW_EN Input | Synthesizer Output |

|-------------|--------------------|

| High        | On                 |

| Low         | Off                |

The switch provides >50 dB isolation at the synthesizer RF output. This allows the SKY73101-11 to be used for GSM applications.

## **Synthesizer Programming**

To program the synthesizer to the correct frequency, values for the N-counter (both M and A portions), fractional divisor (FN), and fractional modulus extender (ME) are needed. These values are used to determine the total divider ratio,  $D_{Total}$ , according to Equation 1:

$$D_{Total} = N_{actual} + FN_{actual} + ME_{actual} + 3.5 \tag{1}$$

Where:  $N_{actual}$  = the actual value of the N-counter

FN<sub>actual</sub> = the actual fractional divisor

$ME_{actual}$  = the actual fractional modulus extender

Because of the way the  $\Delta\Sigma$  modulator is implemented in the SKY73101-11, the number 3.5 must be added to the division number to obtain the final division ratio.

The calculated value for  $D_{Total}$  can then be used to determine the correct synthesizer frequency, RF:

$$RF = \frac{F_{REF}}{RI} \times D_{Total} \tag{2}$$

Where:  $F_{REF}$  = the reference frequency

R1 = the reference divider radio

The 6-bit M-counter and the 4-bit A-counter portions of the N-counter are calculated according to the following relationships:

$N_{actual}$  is the actual N-counter value and is the integer portion of  $(D_{Total} - 3.5)$ :

$$N_{actual} = M_{actual} \times P + A_{actual}$$

(3)

If:  $M = M_{actual}$  (binary number, fit to six bits)

$A = A_{actual}$  (binary number, fit to four bits)

Then:  $N = M \times 2^4 + A$

Where: N is the number to be programmed into the N-counter.

The synthesizer has a selectable prescaler of 8/9 or 16/17. If the 16/17 prescaler is used:

$$P = 2^4 = 16$$

In this case, N is the same as  $N_{actual}$ , M is equal to the six MSBs of  $N_{actual}$ , and A is equal to the four LSBs of  $N_{actual}$ .

If the 8/9 prescaler is used:

$$P = 8$$

Here, N is not equal to  $N_{actual}$ . The A-counter portion only uses the three LSBs (the 4<sup>th</sup> bit of the A-counter is a "don't care" bit).

**NOTE:** The minimum actual N counter value for the 8/9 mode is  $8 \times 7 = 56$ , and for the 16/17 mode is  $16 \times 15 = 240$ .

The fractional divisor code (FN) sets the fractional-N modulo up to 256 modulo according to the following equation:

$$FN_{actual} = D_7 \left(\frac{1}{2}\right) + D_6 \left(\frac{1}{2^2}\right) + D_5 \left(\frac{1}{2^3}\right) + \cdot \cdot + D_0 \left(\frac{1}{2^8}\right)$$

(4)

The value of *FN* is equal to the binary representation of 256 (or  $2^8$ )  $\times$  *FN*<sub>actual</sub>, or:

$$FN = D_7 \times 2^7 + D_6 \times 2^6 + D_5 \times 2^5 + \dots D_0$$

The fractional modulo can be extended up to  $2^{23}$  using the modulo extender (ME) if required:

$$ME_{actual} = D_{14}(1/2^9) + D_{13}(1/2^{10}) + D_{12}(1/2^{11}) + \dots + D_0(1/2^{23})$$

The value of *ME* is equal to the binary representation of the integer part of  $2^{23} \times ME_{actual}$ , or:

$$ME = D_{14} \times 2^{14} + D_{13} \times 2^{13} + D_{12} \times 2^{12} + \dots D_{0}$$

### **Example:**

A desired synthesizer frequency of 1960 MHz is required using a crystal frequency of 52 MHz and an 8/9 prescaler. Since the maximum internal reference frequency is 25 MHz, the crystal frequency needs to be divided; a reference divider ratio of 8 is used for this example.

Restating Equation (2) as a function of  $D_{Totai}$ .

$$D_{Total} = (1960 \times 8)/52 = 301.538461538461$$

Where: RF = 1960

R1 = 8

$F_{RFF} = 52$

Determine  $N_{actual}$  by subtracting 3.5 from  $D_{Total}$  and removing the fractional portion:

$$D_{Total}$$

– 3.5 = 298.038461538461

Using Equation (3):

$$N_{actual} = 298 = M_{actual} \times P + A_{actual}$$

where:  $M_{actual} = 37$

P = 8

$A_{actual} = 2$

$M = M_{actual} = 37 = 100101b$  (the six MSBs)

$A = A_{actual} = 2 = 0010b$  (the four LSBs)

$N = M \times 2^4 + A = 1001010010b$  (the value programmed)

Multiply the fractional portion that was removed in the previous step by 256 and remove the fractional portion of the result to determine *FN*:

$0.038461538461 \times 256 = 9.846153846016$

FN = 9 = 00001001b (the value programmed)

Divide FN by 256 to determine the actual fractional part, FN<sub>actual</sub>.

$FN_{actual} = 9/256 = 0.03515625$

Subtract this result from the fractional portion of  $D_{Total} - 3.5$  to determine the actual fractional modulus extender,  $ME_{actual}$ .

$$ME_{actual} = (D_{Total} - 3.5 - N_{actual}) - FN_{actual}$$

= 0.038461538461 - 0.03515625

= 0.038461538461

Multiply this result by 8388608 (the 23-bit  $\Delta\Sigma$  modulator value, 2<sup>23</sup>) and remove the fractional portion to determine the value of *MF*:

$0.003305288461 \times 8388608 = 27726.769226252288$

ME = 27726 = 110110001001110b (the value programmed). Refer to Tables 6 and 7 for the location of the resulting bits in the ME parameter.

# **Package and Handling Information**

Since the device package is sensitive to moisture absorption, it is baked and vacuum packed before shipping. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The SKY73101-11 is rated to Moisture Sensitivity Level 3 (MSL3) at 260 °C. It can be used for lead or lead-free soldering. For additional information, refer to Skyworks Application Note, *PCB Design and SMT Assembly/Rework Guidelines for MCM-L Packages*, document number 101752.

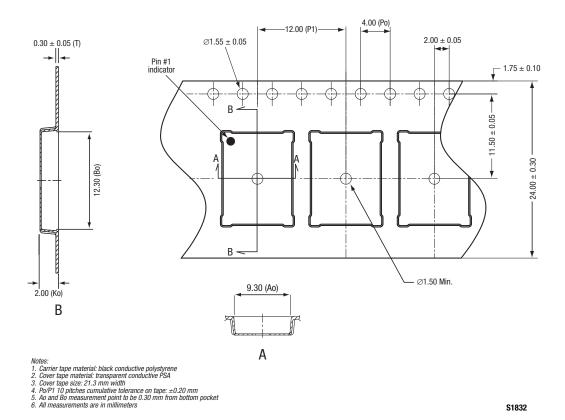

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

# **Circuit Design Considerations**

The following design considerations are general in nature and must be followed regardless of final use or configuration

- 1. Paths to ground should be made as short and as low impedance as possible.

- The ground pad of the SKY73101-11 provides critical electrical grounding requirements. Design the connection to the ground pad to provide the best electrical connection to the circuit board. Multiple vias to the grounding layer are recommended to connect the top layer ground area to the main ground layer.

- Skyworks recommends including external bypass capacitors on the VDD voltage input (pin 37) of the device. These capacitors should be placed as close as possible to the VDD input pin.

- 4. A 50  $\Omega$  impedance trace is needed for the RF\_OUT (pin 10) line.

# **Electrical and Mechanical Specifications**

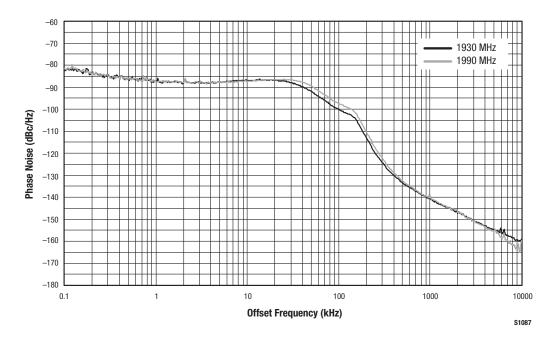

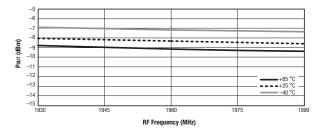

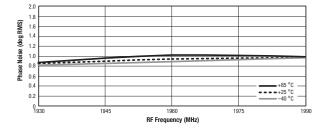

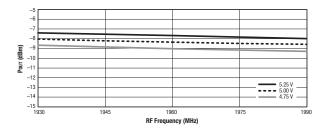

The absolute maximum ratings of the SKY73101-11 are provided in Table 9. The recommended operating conditions are specified in Table 10 and electrical specifications are provided in Table 11. Spur suppression measurements are provided in Table 12. Measurement plots for single sideband phase noise and settling time are shown in Figures 8 and 9, respectively.

Typical performance characteristics of the SKY73101-11 are illustrated in Figures 10 through 27.

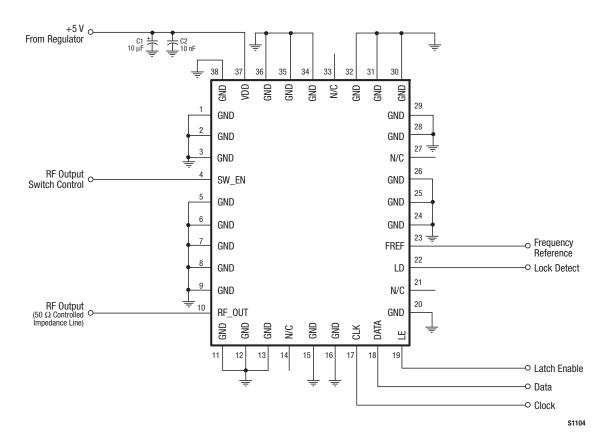

A typical application schematic for the SKY73101-11 is provided in Figure 28. The PCB layout footprint for the SKY73101-11 is provided in Figure 29. Figure 30 shows the package dimensions for the 38-pin MCM and Figure 31 provides the tape and reel dimensions.

# **Electrostatic Discharge (ESD) Sensitivity**

The SKY73101-11 ESD threshold level is 250 VDC for the RF\_OUT pin and 2000 VDC for all other pins using Human Body Model (HBM) testing.

To avoid latent or visible ESD damage, always follow proper ESD handling precautions.

Table 9. SKY73101-11 Absolute Maximum Ratings (Note 1)

| Parameter                     | Symbol | Min | Typical | Max  | Units |

|-------------------------------|--------|-----|---------|------|-------|

| Supply voltage                | VCC    | 0   | 5.0     | 5.5  | V     |

| Input voltage (CLK, DATA, LE) |        | 0   |         | 4.6  | V     |

| Operating temperature         | Тор    | -40 |         | +85  | °C    |

| Storage temperature           | Тѕт    | -40 |         | +150 | °C    |

Note 1: Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal values. Exceeding any of the limits listed here may result in permanent damage to the device.

**CAUTION**: Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times. All pins are rated for a Human Body Model (HBM) Class 1A ESD withstand threshold voltage (250 V).

**Table 10. SKY73101-11 Recommended Operating Conditions**

| Parameter                                                                                           | Symbol         | Min                                                       | Typical | Max        | Units  |

|-----------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------|---------|------------|--------|

| Supply voltage                                                                                      | VCC            | 4.75                                                      | 5.00    | 5.25       | V      |

| Input voltage (CLK, DATA, LE) (Note 1):<br>Low level<br>High level                                  |                | 1.4                                                       | 3.3     | 0.6<br>3.6 | V<br>V |

| Output voltage (LD) with 18 kΩ load from<br>VCC PLL:<br>Low level, unlocked<br>High level, unlocked |                | 2.4                                                       |         | 0.4        | V<br>V |

| Reference frequency input voltage (FREF, pin 23)                                                    | FREFIN         | 0.5                                                       | 1.0     | 1.5        | Vp-p   |

| RF output switch enable: High Low                                                                   | SWENH<br>SWENL | 2.2                                                       |         | 0.8        | V<br>V |

| Load connected to RF output                                                                         |                | 50 $\Omega$ , maximum VSWR (load input) 2.0:1, all phases |         |            |        |

Note 1: The CLK, DATA, and LE signals are internally 3.3 V DC. DO NOT drive these signals to 5 V.

Table 11. SKY73101-11 Electrical Characteristics (Note 1) (Note 2) (VCC = 5 V, Tc = 25 °C, Charge Pump Current = 1600  $\mu$ A, FREF = 52 MHz, Reference Input Divider = 8, Prescale Divider = 8/9, Unless Otherwise Noted)

| Parameter                                                                                                 | Symbol | Test Conditions   | Min  | Typical                                             | Max                                                 | Units                                                              |

|-----------------------------------------------------------------------------------------------------------|--------|-------------------|------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------|

| Oscillation frequency                                                                                     |        |                   | 1930 |                                                     | 1990                                                | MHz                                                                |

| Reference frequency                                                                                       |        |                   |      | 13                                                  | 52                                                  | MHz                                                                |

| Phase detector frequency                                                                                  |        |                   |      | 6.5                                                 |                                                     | MHz                                                                |

| PLL loop bandwidth                                                                                        |        |                   |      | 25                                                  |                                                     | kHz                                                                |

| Output level                                                                                              |        |                   | -10  | -8.6                                                | -6.0                                                | dBm                                                                |

| Output impedance                                                                                          |        |                   |      | 50                                                  |                                                     | Ω                                                                  |

| Output VSWR                                                                                               |        |                   |      |                                                     | 2:1                                                 | -                                                                  |

| Reference frequency input (FREF) impedance                                                                |        |                   | 470  |                                                     |                                                     | Ω                                                                  |

| Harmonic suppression:  2 <sup>nd</sup> harmonic  3 <sup>rd</sup> harmonic                                 |        |                   |      | -46<br>-77                                          | -40<br>-69                                          | dBc<br>dBc                                                         |

| Integrated RMS phase noise                                                                                |        | 100 Hz to 100 kHz |      |                                                     | 1                                                   | degrees RMS                                                        |

| Single sideband phase noise offset:  @ 10 kHz @ 200 kHz @ 400 kHz @ 800 kHz @ 1.8 MHz @ 3.0 MHz @ 6.0 MHz |        |                   |      | -85<br>-121<br>-132<br>-139<br>-146<br>-150<br>-155 | -80<br>-114<br>-124<br>-135<br>-142<br>-146<br>-151 | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz |

| PLL-reference spurious suppression                                                                        |        |                   |      |                                                     | -100                                                | dBc                                                                |

| Frequency settling time                                                                                   |        | Within ±2 kHz     |      | 240                                                 | 375                                                 | μ\$                                                                |

| Phase settling time                                                                                       |        | Within ±5 deg     |      | 272                                                 | 450                                                 | μ\$                                                                |

| Peak phase error                                                                                          |        |                   |      | 1.5                                                 | 5                                                   | degrees                                                            |

| Switch isolation                                                                                          |        |                   | +45  | +47                                                 |                                                     | dBc                                                                |

| Current consumption                                                                                       |        |                   |      | 120                                                 | 135                                                 | mA                                                                 |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

Note 2: Characterized performance may change if the SKY73101-11 is configured differently than the test conditions specified here. This characterization used a 6.5 MHz fixed comparison frequency for the PLL loop filter. The PLL synthesizer is programmable up to a maximum comparison frequency of 26 MHz but with degraded performance.

Table 12. SKY73101-11 Spur Suppression Measurements (VCC = 5 V, Tc = 25 °C, Charge Pump Current = 1600  $\mu$ A, FREF = 52 MHz, Reference Input Divider = 8, Prescale Divider = 8/9, Unless Otherwise Noted)

| Causiana Danay (Idda) | Frequency (MHz)         |                          |                         |  |  |

|-----------------------|-------------------------|--------------------------|-------------------------|--|--|

| Spurious Power (kHz)  | 1930                    | 1960                     | 1990                    |  |  |

| ≥ 200                 | No spur                 | No spur                  | No spur                 |  |  |

| ≥ 400                 | 498.51 kHz,<br>-92 dBc  | No spur                  | No spur                 |  |  |

| ≥ 600                 | No spur                 | No spur                  | No spur                 |  |  |

| ≥ 800                 | No spur                 | No spur                  | No spur                 |  |  |

| ≥ 1000                | 2575.45 kHz,<br>–95 dBc | No spur                  | 1000.00 kHz,<br>–91 dBc |  |  |

| ≥ 3000                | No spur                 | 6515.59 kHz,<br>-100 dBc | No spur                 |  |  |

Figure 8. Single Sideband Phase Noise Measurements

**Figure 9. Phase Settling Time Measurements**

Figure 10. Output Power vs Frequency and Temperature

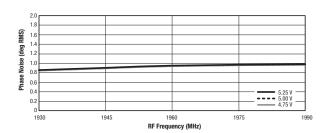

Figure 12. Integrated Phase Noise vs Frequency and Temperature

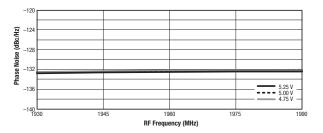

Figure 11. Output Power vs Frequency and Supply Voltage

Figure 13. Integrated Phase Noise vs Frequency and Supply Voltage

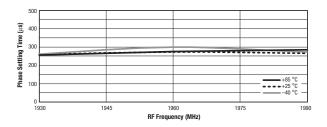

Figure 14. Phase Settling Time vs Frequency and Temperature

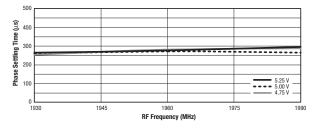

Figure 15. Phase Settling Time vs Frequency and Supply Voltage

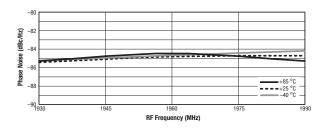

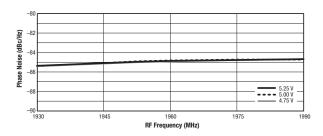

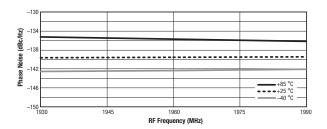

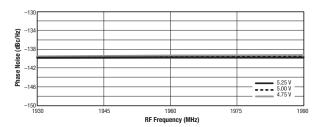

Figure 16. Phase Noise @ 10 kHz Offset vs Frequency and Temperature

Figure 17. Phase Noise @ 10 kHz Offset vs Frequency and Supply Voltage

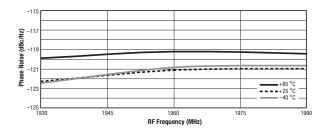

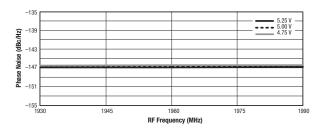

Figure 18. Phase Noise @ 200 kHz Offset vs Frequency and Temperature

Figure 19. Phase Noise @ 200 kHz Offset vs Frequency and Supply Voltage

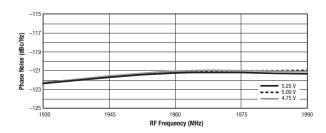

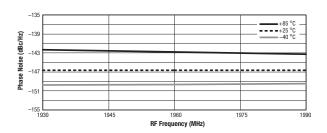

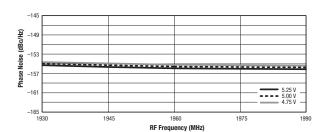

Figure 20. Phase Noise @ 400 kHz Offset vs Frequency and Temperature

Figure 21. Phase Noise @ 400 kHz Offset vs Frequency and Supply Voltage

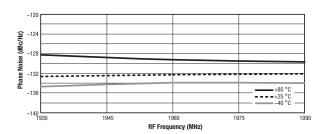

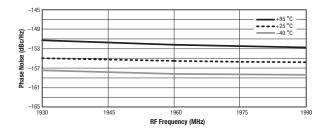

Figure 22. Phase Noise @ 800 kHz Offset vs Frequency and Temperature

Figure 24. Phase Noise @ 1800 kHz Offset vs Frequency and Temperature

Figure 26. Phase Noise @ 6000 kHz Offset vs Frequency and Temperature

Figure 23. Phase Noise @ 800 kHz Offset vs Frequency and Supply Voltage

Figure 25. Phase Noise @ 1800 kHz Offset vs Frequency and Supply Voltage

Figure 27. Phase Noise @ 6000 kHz Offset vs Frequency and Supply Voltage

Figure 28. SKY73101-11 Typical Application Schematic

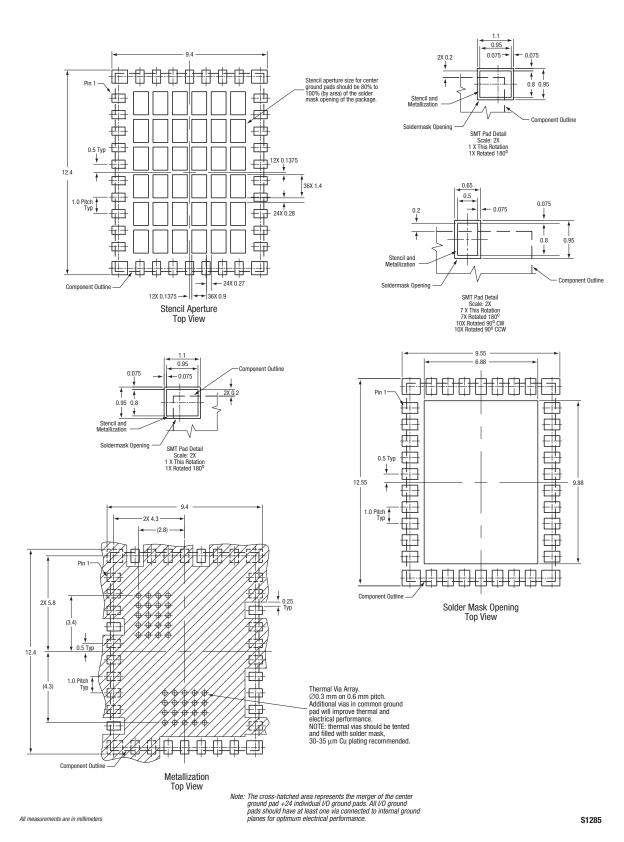

Figure 29. PCB Layout Footprint for the SKY73101-11 9 x 12 mm MCM

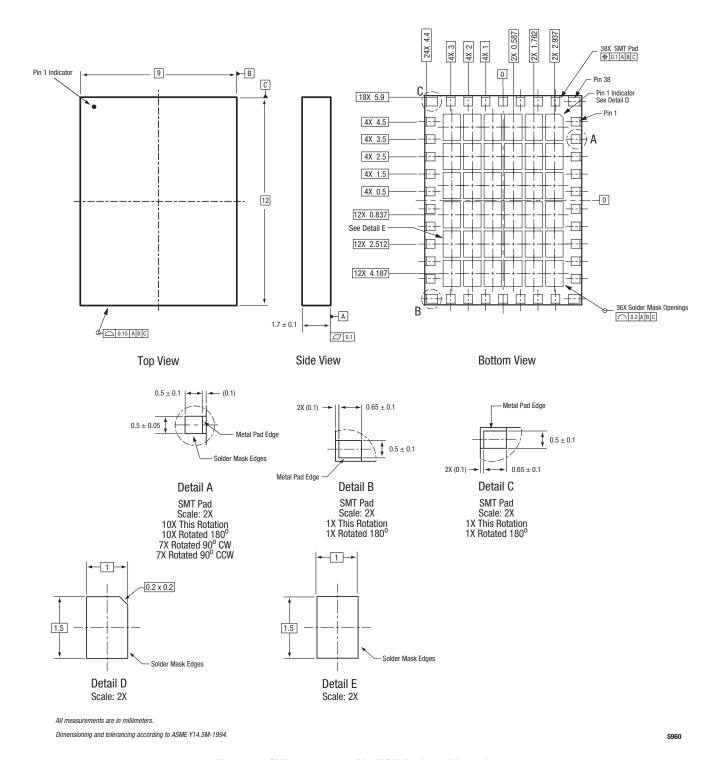

Figure 30. SKY73101-11 38-Pin MCM Package Dimensions

S1832

Figure 31. SKY73101-11 Tape and Reel Dimensions

# **Ordering Information**

| Model Name                                | Manufacturing Part Number | Evaluation Board Part Number |

|-------------------------------------------|---------------------------|------------------------------|

| SKY73101-11 1930-1990 MHz VCO/Synthesizer | SKY73101-11               | TW18-D910                    |

Copyright © 2007, 2008, 2010 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks, the Skyworks symbol, and "Breakthrough Simplicity" are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.