# DATA SHEET

# SKY13551-668LF: 0.4 to 3.8 GHz DP10T (SP5T/SP5T) Main/Receive Diversity Switch with MIPI RFFE Interface for Carrier Aggregation

# **Applications**

- 3G/4G multimode cellular handsets (UMTS, CDMA2000, LTE)

- Carrier aggregation diversity

## **Features**

- Broadband frequency range: 0.4 to 3.8 GHz

- Single, positive DC power supply (2.5 to 4.8 V)

- Integrated, programmable MIPI interface using separate registers for ANT\_A and ANT\_B

- Dual antenna ports can be connected externally to a diplexer

- Small QFN (16-pin, 1.6 x 2.4 x 0.55 mm) package (MSL1, 260 °C per JEDEC J-STD-020)

Skyworks Green<sup>TM</sup> products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green*<sup>TM</sup>, document number SQ04–0074.

## **Description**

The SKY13551-668LF is a dual single-pole, five-throw (2xSP5T) Mobile Industry Processor Interface (MIPI) controlled antenna switch designed specifically for receive diversity in carrier aggregation applications.

The 2xSP5T switch is optimized for broadband performance. Using advanced switching technologies, the SKY13551-668LF maintains low insertion loss and high isolation for all switching paths. The high-linearity performance and low insertion loss achieved by the SKY13551-668LF makes it an ideal choice for carrier aggregation applications in both main and diversity antenna switching. The switch also exhibits excellent second/third order intermodulation distortion (IMD2/IMD3) performance.

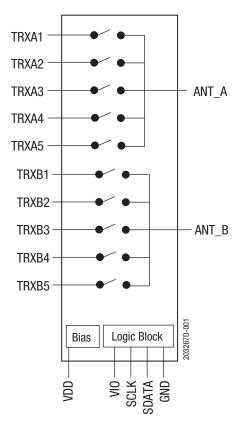

Figure 1. SKY13551-668LF Block Diagram

Switching is controlled by an integrated MIPI decoder. The two switches can be configured independently. There are separate registers for each SP5T switch. No external DC blocking capacitors are required on the RF paths as long as no DC voltage is applied to those paths.

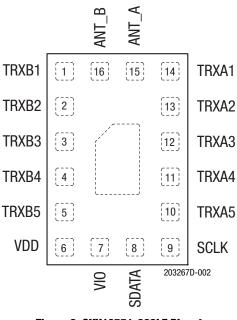

The SKY13551-668LF is manufactured in a compact, 1.6 x 2.4 x 0.55 mm, 16-pin surface-mount Quad Flat No-Lead (QFN) package.

A functional block diagram is shown in Figure 1. The pin configuration and package are shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

Figure 2. SKY13551-668LF Pinout (Top View)

### Table 1. SKY13551-668LF Signal Descriptions<sup>1</sup>

| Pin | Name  | Description                      | Pin | Name  | Description                   |

|-----|-------|----------------------------------|-----|-------|-------------------------------|

| 1   | TRXB1 | Ant B transmit/receive port 1    | 9   | SCLK  | Clock                         |

| 2   | TRXB2 | Ant B transmit/receive port 2    | 10  | TRXA5 | Ant A transmit/receive port 5 |

| 3   | TRXB3 | Ant B transmit/receive port 3    | 11  | TRXA4 | Ant A transmit/receive port 4 |

| 4   | TRXB4 | Ant B transmit/receive port 4    | 12  | TRXA3 | Ant A transmit/receive port 3 |

| 5   | TRXB5 | Ant B transmit/receive port 5    | 13  | TRXA2 | Ant A transmit/receive port 2 |

| 6   | VDD   | DC power supply                  | 14  | TRXA1 | Ant A transmit/receive port 1 |

| 7   | VIO   | MIPI interface DC supply voltage | 15  | ANT_A | Ant A port                    |

| 8   | SDATA | Data                             | 16  | ANT_B | Ant B port                    |

<sup>1</sup> Bottom ground paddles must be connected to ground.

# **Electrical and Mechanical Specifications**

The absolute maximum ratings of the SKY13551-668LF are provided in Table 2. Electrical specifications are provided in Tables 3 and 4.

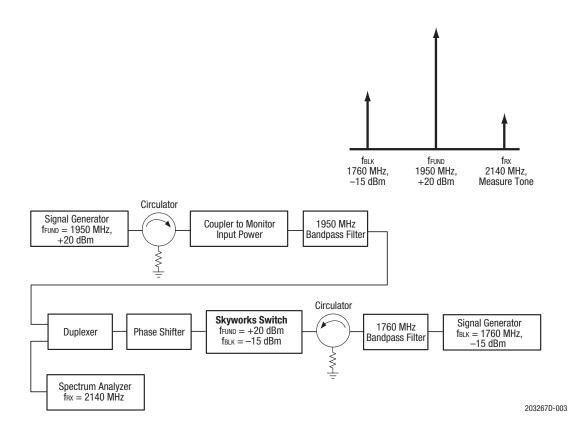

IMD2 and IMD3 test conditions for various frequencies are listed in Tables 5 and 6, respectively.

Figure 3 illustrates the test setup used to measure intermodulation products. This industry standardized test is used to simulate the WCDMA linearity of the antenna switch. A +20 dBm continuous wave (CW) signal, fFUND, is sequentially applied to the TRX ports, while a -15 dBm CW blocker signal, fBLK, is applied to the ANT port.

The resulting third order intermodulation distortion (IMD3), fRx, is measured over all phases of fFUND. The SKY13551-668LF exhibits exceptional performance for all RF ports.

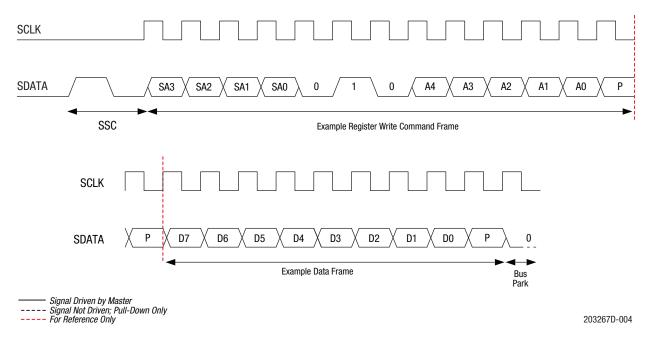

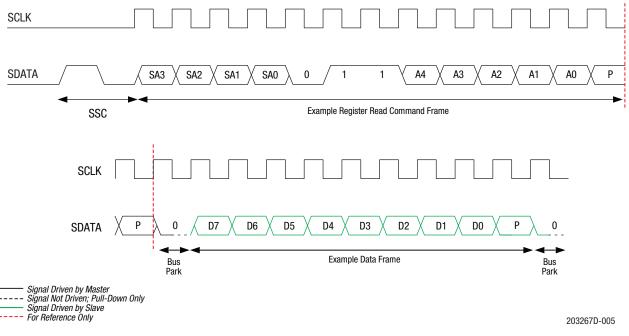

Table 7 describes the register content and programming read/write sequences. Refer to the *MIPI Alliance Specification for RF Front-End Control Interface (RFFE)*, v1.10 (26 July 2011) for additional information on MIPI programming sequences and MIPI bus specifications.

Figure 4 provides the timing diagram for register write commands. Figure 5 provides the timing diagram for register read commands.

Register descriptions and programming information is provided in Table 8. Tables 9 and 10 provide the Register\_0 and Register\_1 logic, respectively.

#### Table 2. SKY13551-668LF Absolute Maximum Ratings<sup>1</sup>

| Parameter              | Symbol | Minimum | Maximum | Units |

|------------------------|--------|---------|---------|-------|

| Supply voltage         | Vdd    | 2.5     | 5.0     | V     |

| Digital control signal | Vio    |         | 2       | V     |

| SCLK port voltage      | VSCLK  |         | Vio     | V     |

| SDATA port voltage     | VSDATA |         | Vio     | V     |

| LTE input power        | Pin    |         | +31     | dBm   |

| Storage temperature    | Тѕтс   | -55     | +150    | °C    |

| Operating temperature  | Тор    | -30     | +90     | °C    |

<sup>1</sup> Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

**CAUTION**: Although this device is designed to be as robust as possible, electrostatic discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times.

| Parameter                                                 | Symbol   | Test Condition                                                                        | Min | Typical | Max  | Units |

|-----------------------------------------------------------|----------|---------------------------------------------------------------------------------------|-----|---------|------|-------|

| Operating frequency                                       | f        |                                                                                       | 0.4 |         | 3.8  | GHz   |

| Insertion loss                                            | IL       | ANT_A to any TRxA port<br>ANT_B to any TRxB port:                                     |     |         |      |       |

|                                                           |          | 400 to 824 MHz                                                                        |     | 0.40    | 0.60 | dB    |

|                                                           |          | 824 to 960 MHz                                                                        |     | 0.45    | 0.60 | dB    |

|                                                           |          | 1427 to 1511 MHz                                                                      |     | 0.5     | 0.7  | dB    |

|                                                           |          | 1710 to 2170 MHz                                                                      |     | 0.80    | 1.0  | dB    |

|                                                           |          | 2170 to 2690 MHz                                                                      |     | 1.0     | 1.2  | dB    |

|                                                           |          | 3400 to 3800 MHz                                                                      |     | 1.3     | 1.6  | dB    |

| Isolation                                                 | ISO      | ANT_A or ANT_B to any "off" TRx port:                                                 |     |         |      |       |

|                                                           |          | Up to 787 MHz                                                                         | 31  | 34      |      | dB    |

|                                                           |          | Up to 960 MHz                                                                         | 30  | 33      |      | dB    |

|                                                           |          | Up to 1511 MHz                                                                        | 24  | 29      |      | dB    |

|                                                           |          | Up to 1990 MHz                                                                        | 22  | 25      |      | dB    |

|                                                           |          | Up to 2170 MHz                                                                        | 21  | 24      |      | dB    |

|                                                           |          | Up to 2690 MHz                                                                        | 18  | 21      |      | dB    |

|                                                           |          | Up to 3800 MHz                                                                        | 15  | 18      |      | dB    |

|                                                           |          | ANT_A to any TRxB port<br>ANT_B to any TRxA port:                                     |     |         |      |       |

|                                                           |          | Up to 787 MHz                                                                         | 40  | 42      |      | dB    |

|                                                           |          | Up to 960 MHz                                                                         | 38  | 40      |      | dB    |

|                                                           |          | Up to 1511 MHz                                                                        | 34  | 37      |      | dB    |

|                                                           |          | Up to 1990 MHz                                                                        | 32  | 33      |      | dB    |

|                                                           |          | Up to 2170 MHz                                                                        | 31  | 32      |      | dB    |

|                                                           |          | Up to 2690 MHz                                                                        | 29  | 30      |      | dB    |

|                                                           |          | Up to 3800 MHz                                                                        | 26  | 27      |      | dB    |

|                                                           |          | ANT_A to ANT_B:                                                                       |     |         |      |       |

|                                                           |          | 400 to 960 MHz                                                                        | 31  | 32      |      | dB    |

|                                                           |          | 1427 to 1511 Mhz                                                                      | 26  | 28      |      | dB    |

|                                                           |          | 1710 to 1990 MHz                                                                      | 25  | 26      |      | dB    |

|                                                           |          | 1980 to 2690 MHz                                                                      | 22  | 23      |      | dB    |

|                                                           |          | 3400 to 3800 MHz                                                                      | 18  | 19      |      | dB    |

| "On" state match                                          | VSWR     | 400 to 2170 MHz                                                                       |     | 1.6:1   | 2:1  |       |

| Second order intermodulation distortion                   | IMD2     | See Table 5                                                                           |     | -105    | -100 | dBm   |

| Third order intermodulation distortion                    | IMD3     | See Table 6                                                                           |     | -105    | -100 | dBm   |

| Low-band 2 <sup>nd</sup> and 3 <sup>rd</sup> harmonic     | 2fo, 3fo | Any TRx port, $PIN = +26 \text{ dBm}$ , f = 900 MHz                                   |     | -70     | -64  | dBm   |

|                                                           |          | Any TRx port, $PIN = +26 \text{ dBm}$ , $f0 = 900 \text{ MHz}$ , $VSWR = 5:1$         |     | -65     | -60  | dBm   |

| Middle-band 2 <sup>nd</sup> and 3 <sup>rd</sup> harmonics | 2fo, 3fo | Any TRxA and any TRxB port, $P_{IN} = +26 \text{ dBm}$ , f1 = 1462 MHz, f2 = 1910 MHz |     | -70     | -65  | dBm   |

|                                                           |          | Any TRxA and any TRxB port, PIN = $+26$ dBm, f1 = 1462 MHz, f2 = 1910 MHz, VSWR = 5:1 |     | -65     | 58   | dBm   |

| High-band 2 <sup>nd</sup> and 3 <sup>rd</sup> harmonic    | 2fo, 3fo | Any TRxA and any TRxB port,<br>PiN = +26 dBm, f0 = 2690 MHz                           |     | -61     | -55  | dBm   |

|                                                           |          | Any TRxA and any TRxB port,<br>Piℕ = +26 dBm, f0 = 2690 MHz, VSWR = 5:1               |     | -59     | -53  | dBm   |

## Table 3. SKY13551-668LF RF Electrical Specifications<sup>1</sup> (1 of 2) (Vod = 2.85 V, Top = +25 °C, Characteristic Impedance [Zo] = 50 $\Omega$ , Unless Otherwise Noted)

| Parameter                        | Symbol | Test Condition                                                       | Test Condition Min |     |    |     |  |  |  |  |

|----------------------------------|--------|----------------------------------------------------------------------|--------------------|-----|----|-----|--|--|--|--|

| Band 13 2 <sup>nd</sup> harmonic | 2fo    | Any TRx port, $PIN = +25 \text{ dBm}$ , $f0 = 782 \text{ MHz}$       |                    | -77 |    | dBm |  |  |  |  |

| Band 17 3 <sup>rd</sup> harmonic | 3fo    | Any TRx port, $PIN = +25 \text{ dBm}$ , f = 707 MHz                  |                    | -77 |    | dBm |  |  |  |  |

| Turn-on time                     | ton    | From application of VDD and VIO or<br>transition from low power mode |                    |     | 20 | μs  |  |  |  |  |

| Wake-up time                     | tw     | From isolation state                                                 |                    | 2   | 5  | μs  |  |  |  |  |

| Switching speed                  | tsw    | Any state to any other state                                         |                    | 2   | 5  | μs  |  |  |  |  |

#### Table 3. SKY13551-668LF RF Electrical Specifications<sup>1</sup> (2 of 2) (Vop = 2.85 V. Top = +25 °C. Characteristic Impedance [Zo] = 50 $\Omega$ . Unless Otherwise Noted)

<sup>1</sup> Performance is guaranteed only under the conditions listed in this table.

# Table 4. SKY13551-668LF DC Electrical Specifications<sup>1</sup>(VDD = 2.85 V, Vio = 1.8 V, Top = +25 °C, Characteristic Impedance [Zo] = 50 $\Omega$ , Unless Otherwise Noted)

| Parameter                                      | Symbol        | Test Condition | Min              | Typical | Max                | Units  |

|------------------------------------------------|---------------|----------------|------------------|---------|--------------------|--------|

| Supply voltage                                 | Vdd           |                | 2.50             | 2.85    | 4.8                | ۷      |

| Supply current, active mode                    | IDD           |                |                  | 35      | 100                | μA     |

| Interface supply voltage level                 | Vio           |                | 1.65             | 1.80    | 1.95               | V      |

| Digital data and clock signals:<br>High<br>Low | Vsdata, Vsclk |                | 0.8	imes Vio $0$ |         | Vio $0.2	imes$ Vio | V<br>V |

| Interface supply current                       | Ινιο          |                |                  | 5       | 50                 | μA     |

<sup>1</sup> Performance is guaranteed only under the conditions listed in this table.

### **Table 5. IMD2 Test Conditions**

| Band  | Transmit<br>Frequency<br>(MHz) | Transmit Power<br>(dBm) | Frequency Blocker,<br>Low<br>(MHz) | Frequency Blocker,<br>High<br>(MHz) | Power Blocker<br>(dBm) | Receive Frequency<br>(MHz) |

|-------|--------------------------------|-------------------------|------------------------------------|-------------------------------------|------------------------|----------------------------|

| 1     | 1950                           |                         | 190                                | 4090                                |                        | 2140                       |

| 2     | 1880                           |                         | 80                                 | 3840                                |                        | 1960                       |

| 4     | 1732                           |                         | 400                                | 3864                                |                        | 2132                       |

| 5     | 836.5                          | +20                     | 45                                 | 1718                                | -15                    | 881.5                      |

| 7     | 2535                           |                         | 120                                | 5187                                |                        | 2655                       |

| 8     | 897                            |                         | 45                                 | 1839                                |                        | 942                        |

| 11/21 | 1452                           |                         |                                    | 2952                                |                        | 1500                       |

## Table 6. IMD3 Test Conditions

| Band  | Transmit Frequency<br>(MHz) | Transmit Power<br>(dBm) | Frequency Blocker<br>(MHz) | Power Blocker<br>(dBm) | Receive Frequency<br>(MHz) |

|-------|-----------------------------|-------------------------|----------------------------|------------------------|----------------------------|

| 1     | 1950                        |                         | 1760                       |                        | 2140                       |

| 2     | 1880                        |                         | 1800                       |                        | 1960                       |

| 4     | 1732                        |                         | 1332                       |                        | 2132                       |

| 5     | 836.5                       | +20                     | 791.5                      | -15                    | 881.5                      |

| 7     | 2535                        |                         | 2415                       |                        | 2655                       |

| 8     | 897                         |                         | 852                        |                        | 942                        |

| 11/21 | 1452                        |                         | 1404                       |                        | 1500                       |

Figure 3. Typical Third Order Intermodulation Test Setup

|                                     |     |         |    |           |         |           |                |     | Extended Operation |                |     |                   |                |     |

|-------------------------------------|-----|---------|----|-----------|---------|-----------|----------------|-----|--------------------|----------------|-----|-------------------|----------------|-----|

| Туре                                | SSC | C11-C8  | C7 | C6-C5     | C4      | C3-C0     | Parity<br>Bits | BPC | DA7(1)-<br>DA0(1)  | Parity<br>Bits | BPC | DA7(n)-<br>DA0(n) | Parity<br>Bits | BPC |

| Reg_0<br>Write,<br>Short<br>Command | Y   | SA[3:0] | 1b | Data[6:5] | Data[4] | Data{3:0] | Y              | Y   | _                  | -              | -   | -                 | -              | -   |

| Reg_0<br>Write,<br>Long<br>Command  | Y   | SA[3:0] | 0  | 10b       | Addr[4] | Addr[3:0] | Y              | _   | Data[7:0]          | _              | _   | -                 | Y              | Y   |

| Reg_1<br>Write                      | Y   | SA[3:0] | 0  | 10b       | Addr[4] | Addr[3:0] | Y              | -   | Data[7:0]          | -              | -   | -                 | Y              | Y   |

| Reg<br>Read                         | Y   | SA[3:0] | 0  | 11b       | Addr[4] | Addr[3:0] | Y              | Y   | Data[7:0]          | -              | _   | _                 | Y              | Y   |

#### **Table 7. Command Sequence Bit Definitions**

Legend:

SSC = Sequence start commandC = Command frame bits

DA = Data/address frame bits BPC = Bus park cycle BC = Byte count (# of consecutive addresses)

#### DATA SHEET • SKY13551-668LF: MAIN/RECEIVE DIVERSITY SWITCH FOR CARRIER AGGREGATION

Figure 4. Register Write Command Timing Diagram

Figure 5. Register Read Command Timing Diagram

| Register            |                  |                 |                                                                                                                                                                                            |                     |  |

|---------------------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| Name                | Address<br>(Hex) | Parameter       | Description                                                                                                                                                                                | Default<br>(Binary) |  |

| Register_0          | 0000             | MODE_CTRL       | Bits[6:0]:                                                                                                                                                                                 | 0000000             |  |

|                     |                  |                 | See Table 10 for logic                                                                                                                                                                     |                     |  |

| Register_1          | 0001             | MODE_CTRL       | Bits[7:0]:                                                                                                                                                                                 | 00000000            |  |

|                     |                  |                 | See Table 11 for logic                                                                                                                                                                     |                     |  |

|                     |                  | PWR_MODE        | Bits[7:6]:                                                                                                                                                                                 | 00                  |  |

|                     |                  |                 | 00 = Normal operation (active)<br>01 = Default settings (startup)<br>10 = Low power (low power)<br>11 = Reserved                                                                           |                     |  |

|                     |                  | Trigger_Mask_2  | Bit[5]:                                                                                                                                                                                    | 0                   |  |

|                     |                  |                 | If this bit is set, trigger 2 is disabled. When all triggers are disabled, if writing to a register that is associated with trigger 2, the data goes directly to the destination register. |                     |  |

|                     |                  | Trigger_Mask_1  | Bit[4]:                                                                                                                                                                                    | 0                   |  |

| PM_TRIG<br>(Note 1) | 001C             |                 | If this bit is set, trigger 1 is disabled. When all triggers are disabled, if writing to a register that is associated with trigger 1, the data goes directly to the destination register. |                     |  |

| ( )                 |                  | Trigger_Mask_0  | Bit[3]:                                                                                                                                                                                    | 0                   |  |

|                     |                  |                 | If this bit is set, trigger 0 is disabled. When all triggers are disabled, if writing to a register that is associated with trigger 0, the data goes directly to the destination register. |                     |  |

|                     |                  | Trigger_2       | Bit[2]:                                                                                                                                                                                    | 0                   |  |

|                     |                  |                 | If this bit is set, data is loaded into the trigger 2 registers.                                                                                                                           |                     |  |

|                     |                  | Trigger_1       | Bit[1]:                                                                                                                                                                                    | 0                   |  |

|                     |                  |                 | If this bit is set, data is loaded into the trigger 1 registers.                                                                                                                           |                     |  |

|                     |                  | Trigger_0       | Bit[0]:                                                                                                                                                                                    | 0                   |  |

|                     |                  |                 | If this bit is set, data is loaded into the trigger 0 registers.                                                                                                                           |                     |  |

| PRODUCT_ID          | 001D             | PRODUCT_ID      | Bits[7:0]:                                                                                                                                                                                 | 11010110            |  |

|                     |                  |                 | This is a read-only register. However, during the programming of the Unique Slave Identifier (USID), a write command sequence is performed on this register but the value is not changed.  |                     |  |

| MANUFACTURER_ID     | 001E             | MANUFACTURER_ID | Bits[7:0]:                                                                                                                                                                                 | 10100101            |  |

|                     |                  |                 | Read-only register                                                                                                                                                                         |                     |  |

|                     |                  | Reserved        | Bits[7:6]:                                                                                                                                                                                 | 00                  |  |

|                     |                  |                 | Reserved                                                                                                                                                                                   |                     |  |

| MAN LIGID           | 001F             | MANUFACTURER_ID | Bits[5:4]:                                                                                                                                                                                 | 01                  |  |

| MAN_USID            | UUIF             |                 | Read-only register                                                                                                                                                                         |                     |  |

|                     |                  | USID            | Bits[3:0]:                                                                                                                                                                                 | 1010                |  |

|                     |                  |                 | Programmable USID. A write to these bits programs the USID.                                                                                                                                |                     |  |

#### **Table 8. Register Description and Programming**

<sup>1</sup> Unlike the complete independence between triggers 0, 1, and 2, and also between the associated trigger masks 0, 1, and 2, respectively, as described in the MIPI RFFE Specification, this device uses additional interactions between the provided trigger functions.

The delayed application of updated data to all triggerable registers in this device may be accomplished using any of the three triggers (0, 1, or 2), provided that the particular trigger used is not currently masked off. If multiple triggers are enabled, any or all of those are sufficient to cause the data to be transferred from shadow registers to destination registers for all triggerable registers in the device.

It is also necessary to disable all three triggers (i.e., set all three trigger masks) to ensure that data written to any triggerable register will immediately be written to the destination register at the conclusion of the RFFE command sequence where the data is written.

## Table 9. Register\_0 Truth Table (Ant B)

|               |    |    |    | Registe | er 0 Bits |    |    |    |

|---------------|----|----|----|---------|-----------|----|----|----|

| On State      | D7 | D6 | D5 | D4      | D3        | D2 | D1 | DO |

| All isolation |    |    |    | 0       | 0         | 0  | 0  | 0  |

| TRxB1         |    |    |    | 0       | 0         | 0  | 0  | 1  |

| TRxB2         |    |    |    | 0       | 0         | 0  | 1  | 0  |

| TRxB3         |    |    |    | 0       | 0         | 0  | 1  | 1  |

| TRxB4         |    |    |    | 0       | 0         | 1  | 0  | 0  |

| TRxB5         |    |    |    | 0       | 0         | 1  | 0  | 1  |

| Isolation     |    |    |    | 0       | 0         | 1  | 1  | 0  |

| TRxB5         |    |    |    | 0       | 0         | 1  | 1  | 1  |

| TRxB4         |    |    |    | 0       | 1         | 0  | 0  | 0  |

| TRxB3         |    |    |    | 0       | 1         | 0  | 0  | 1  |

| TRxB2         |    |    |    | 0       | 1         | 0  | 1  | 0  |

| TRxB1         |    |    |    | 0       | 1         | 0  | 1  | 1  |

| TRxB5+4       |    |    |    | 0       | 1         | 1  | 0  | 0  |

| TRxB5+3       |    |    |    | 0       | 1         | 1  | 0  | 1  |

| TRxB5+2       |    |    |    | 0       | 1         | 1  | 1  | 0  |

| TRxB5+1       |    |    |    | 0       | 1         | 1  | 1  | 1  |

| TRxB4+3       |    |    |    | 1       | 0         | 0  | 0  | 0  |

| TRxB4+2       |    |    |    | 1       | 0         | 0  | 0  | 1  |

| TRxB4+1       |    |    |    | 1       | 0         | 0  | 1  | 0  |

| TRxB3+2       |    |    |    | 1       | 0         | 0  | 1  | 1  |

| TRxB3+1       |    |    |    | 1       | 0         | 1  | 0  | 0  |

| TRxB2+1       |    |    |    | 1       | 0         | 1  | 0  | 1  |

| All isolation |    |    |    | 1       | 0         | 1  | 1  | 0  |

| All isolation |    |    |    | 1       | 0         | 1  | 1  | 1  |

| All isolation |    |    |    | 1       | 1         | 0  | 0  | 0  |

| All isolation |    |    |    | 1       | 1         | 0  | 0  | 1  |

| All isolation |    |    |    | 1       | 1         | 0  | 1  | 0  |

| All isolation |    |    |    | 1       | 1         | 0  | 1  | 1  |

| All isolation |    |    |    | 1       | 1         | 1  | 0  | 0  |

| All isolation |    |    |    | 1       | 1         | 1  | 0  | 1  |

| All isolation |    |    |    | 1       | 1         | 1  | 1  | 0  |

| All isolation |    |    |    | 1       | 1         | 1  | 1  | 1  |

## Table 10. Register\_1 Truth Table (Band A)

|               |    | Register 0 Bits |    |    |    |    |    |    |  |

|---------------|----|-----------------|----|----|----|----|----|----|--|

| On State      | D7 | D6              | D5 | D4 | D3 | D2 | D1 | DO |  |

| All isolation |    |                 |    | 0  | 0  | 0  | 0  | 0  |  |

| TRxA1         |    |                 |    | 0  | 0  | 0  | 0  | 1  |  |

| TRxA2         |    |                 |    | 0  | 0  | 0  | 1  | 0  |  |

| TRxA3         |    |                 |    | 0  | 0  | 0  | 1  | 1  |  |

| TRxA4         |    |                 |    | 0  | 0  | 1  | 0  | 0  |  |

| TRxA5         |    |                 |    | 0  | 0  | 1  | 0  | 1  |  |

| Isolation     |    |                 |    | 0  | 0  | 1  | 1  | 0  |  |

| TRxA5         |    |                 |    | 0  | 0  | 1  | 1  | 1  |  |

| TRxA4         |    |                 |    | 0  | 1  | 0  | 0  | 0  |  |

| TRxA3         |    |                 |    | 0  | 1  | 0  | 0  | 1  |  |

| TRxA2         |    |                 |    | 0  | 1  | 0  | 1  | 0  |  |

| TRxA1         |    |                 |    | 0  | 1  | 0  | 1  | 1  |  |

| TRxA5+4       |    |                 |    | 0  | 1  | 1  | 0  | 0  |  |

| TRxA5+3       |    |                 |    | 0  | 1  | 1  | 0  | 1  |  |

| TRxA5+2       |    |                 |    | 0  | 1  | 1  | 1  | 0  |  |

| TRxA5+1       |    |                 |    | 0  | 1  | 1  | 1  | 1  |  |

| TRxA4+3       |    |                 |    | 1  | 0  | 0  | 0  | 0  |  |

| TRxA4+2       |    |                 |    | 1  | 0  | 0  | 0  | 1  |  |

| TRxA4+1       |    |                 |    | 1  | 0  | 0  | 1  | 0  |  |

| TRxA3+2       |    |                 |    | 1  | 0  | 0  | 1  | 1  |  |

| TRxA3+1       |    |                 |    | 1  | 0  | 1  | 0  | 0  |  |

| TRxA2+1       |    |                 |    | 1  | 0  | 1  | 0  | 1  |  |

| All isolation |    |                 |    | 1  | 0  | 1  | 1  | 0  |  |

| All isolation |    |                 |    | 1  | 0  | 1  | 1  | 1  |  |

| All isolation |    |                 |    | 1  | 1  | 0  | 0  | 0  |  |

| All isolation |    |                 |    | 1  | 1  | 0  | 0  | 1  |  |

| All isolation |    |                 |    | 1  | 1  | 0  | 1  | 0  |  |

| All isolation |    |                 |    | 1  | 1  | 0  | 1  | 1  |  |

| All isolation |    |                 |    | 1  | 1  | 1  | 0  | 0  |  |

| All isolation |    |                 |    | 1  | 1  | 1  | 0  | 1  |  |

| All isolation |    |                 |    | 1  | 1  | 1  | 1  | 0  |  |

| All isolation |    |                 |    | 1  | 1  | 1  | 1  | 1  |  |

# **Evaluation Board Description**

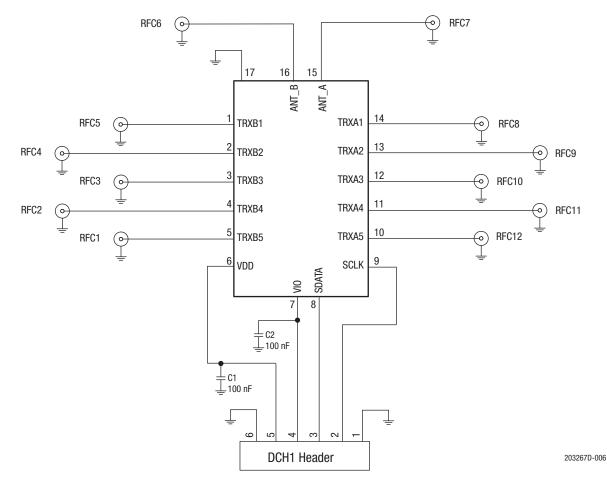

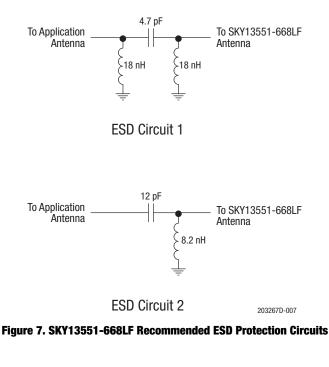

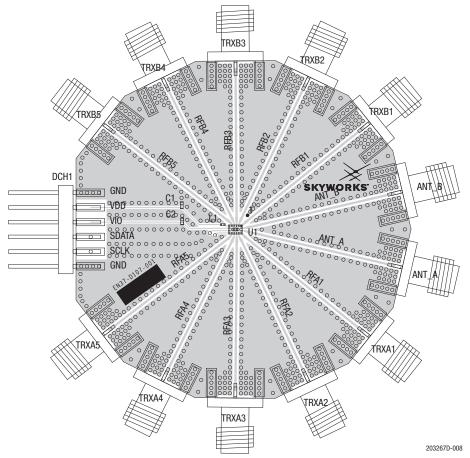

The SKY13551-668LF Evaluation Board is used to test the performance of the SKY13551-668LF DP10T Switch. An Evaluation Board schematic diagram is provided in Figure 6. A recommended ESD protection circuit diagram is provided in Figure 7. An assembly drawing for the Evaluation Board is shown in Figure 8.

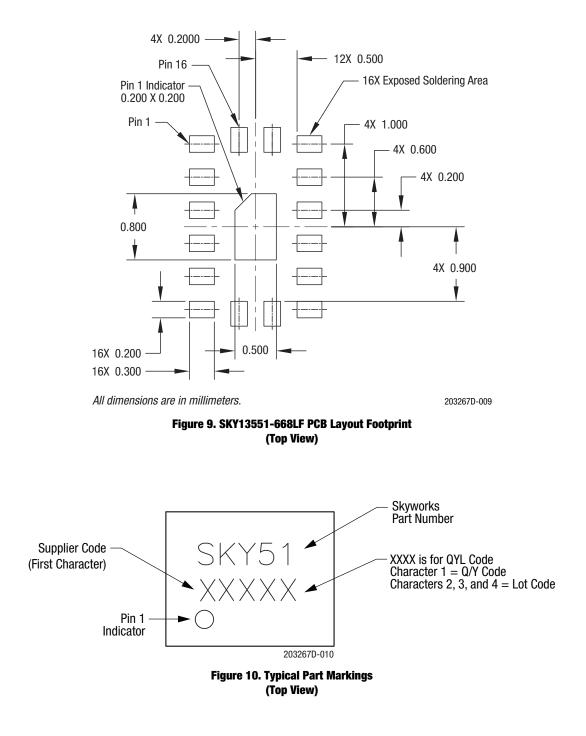

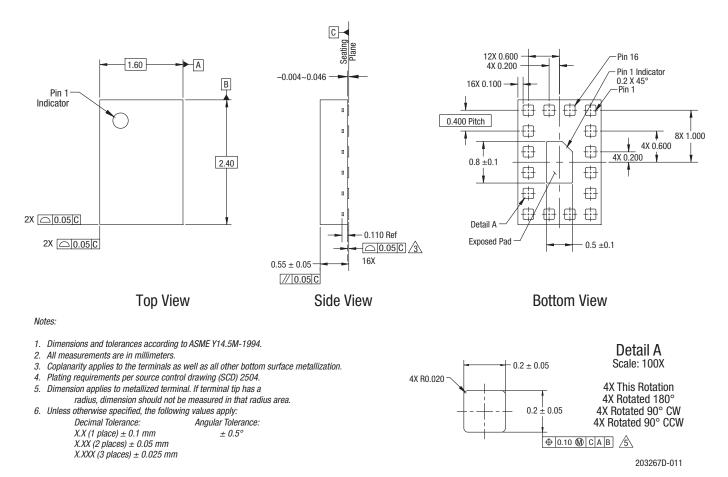

## **Package Dimensions**

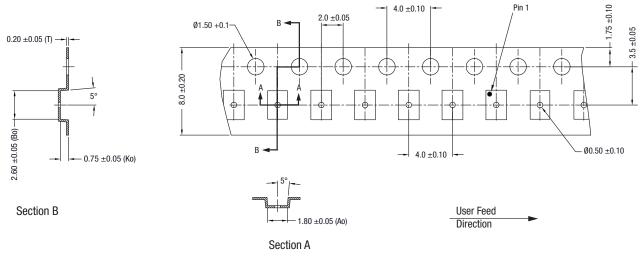

The PCB layout footprint for the SKY13551-668LF is provided in Figure 9. Typical part markings are shown in Figure 10. Package dimensions are shown in Figure 11, and tape and reel dimensions are provided in Figure 12.

# **Package and Handling Information**

Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The SKY13551-668LF is rated to Moisture Sensitivity Level 1 (MSL1) at 260 °C. It can be used for lead or lead-free soldering. For additional information, refer to the Skyworks Application Note, *Solder Reflow Information*, document number 200164.

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

Figure 6. SKY13551-668LF Evaluation Board Schematic

Figure 8. SKY13551-668LF Evaluation Board Assembly Diagram

#### DATA SHEET • SKY13551-668LF: MAIN/RECEIVE DIVERSITY SWITCH FOR CARRIER AGGREGATION

#### Notes:

- Carrier tape material: black conductive polystyrene or polycarbonate.

Cover tape material: transparent conductive.

ESD surface resistivity shall be ≤1 x 10<sup>10</sup> Ohms/square per EIA, JEDEC TNR specification.

10-sprocket hole pitch cumulative tolerance: ±0.20 mm.

- 5. Ao and Bo measured on plane 0.30 mm above the bottom of the pocket.

- 6. All dimensions are in millimeters.

203267D-012

#### Figure 12. SKY13551-668LF Tape and Reel Dimensions

## **Ordering Information**

| Model Name                                  | Manufacturing Part Number | Evaluation Board Part Number |  |  |

|---------------------------------------------|---------------------------|------------------------------|--|--|

| SKY13551-668LF: 0.4 to 3.8 GHz DP10T Switch | SKY13551-668LF            | SKY13551-668LF-EVB           |  |  |

Copyright © 2014-2016 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks and the Skyworks symbol are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.