# AN951: Driving Long Traces on PCIe Backplanes for Simple Evaluation

It is becoming common in server and storage applications to require more than twenty 100 MHz PCIe Gen 2/3 clock outputs for various system functions and ICs. Along with this high fan-out count, designing clock traces longer than ten inches and hybrid models driving high speed cables over HSMC connectors in addition to long traces are becoming increasingly common. In these design cases, designers are always concerned about jitter margin and performance, receiver signal integrity requirements that the driver needs to satisfy, and the impact of aggressor signals on PCIe jitter performance.

This application note analyzes different real world PCIe circuit designs and how different trace lengths, trace impedance, and aggressors will impact signal integrity and jitter performance. The analysis is done using evaluation boards designed to closely replicate the different scenarios of the circuit design mentioned above.

#### KEY EVB FEATURES

- Two types of traces:

- Traces on the top layer of a 6-layer PCB.

Traces in the middle layer (layer 3) of a 6-layer PCB.

- 100 Ω differential impedance trace (Z<sub>0</sub> = 50 Ω).

- 85  $\Omega$  differential impedance trace (Z<sub>0</sub> = 42.5  $\Omega$ ).

- An aggressor signal along with the PCIe clock signal.

- HSMC connectors for high speed cables instead of driving the traces on the board.

AN951: Driving Long Traces on PCIe Backplanes for Simple Evaluation • Overview

#### 1. Overview

Figure 1.1 Example of the Evaluation Boards Used on page 2 is an example of the evaluation boards. Each board has labels describing the trace type, total trace length, and the differential trace impedance.

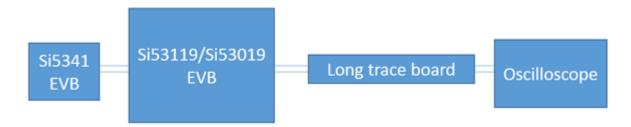

Figure 1.2 Measurement Setup on page 2 shows the block diagram for the measurement setup.

Figure 1.1. Example of the Evaluation Boards Used

It should be noted that the analysis in this application note is based on the data taken with the Si53119 PCIe buffer device with Si5341 as the clock source. However, similar performance can be expected using any PCIe clock generator/buffer IC noted in the table below.

| Table 1.1. | Skyworks | <b>PCIe Server</b> | Buffer Family |

|------------|----------|--------------------|---------------|

|------------|----------|--------------------|---------------|

| Part Number | Outputs | Output Buffer Type |

|-------------|---------|--------------------|

| Si53106     | 6       | Push-Pull          |

| Si53108     | 8       | Push-Pull          |

| Si53112     | 12      | Push-Pull          |

| Si53115     | 15      | Push-Pull          |

| Si53119     | 19      | Push-Pull          |

| Si53019     | 19      | Constant Current   |

Two common analyses are:

1. Push-pull versus current mode HCSL output buffer designs, as covered in AN871: "Driving Long PCIe Clock Lines" (100 Ω differential impedance).

2. Impact of trace length for 85  $\Omega$  impedance traces, as covered in this application note (push-pull buffer design).

AN951: Driving Long Traces on PCIe Backplanes for Simple Evaluation • Impact of Trace Length for 85 Ω Impedance Traces (Push-pull Buffer Design)

### 2. Impact of Trace Length for 85 Ω Impedance Traces (Push-pull Buffer Design)

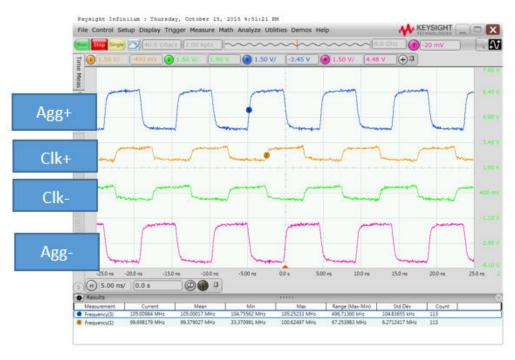

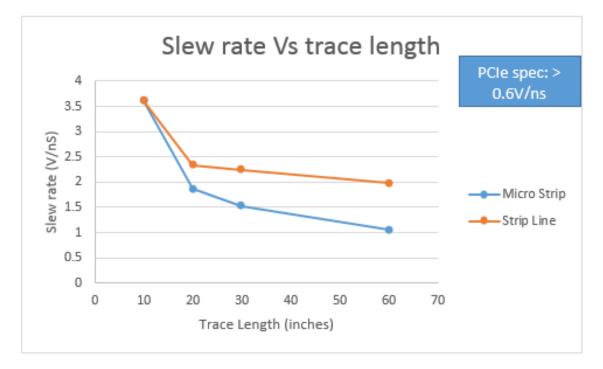

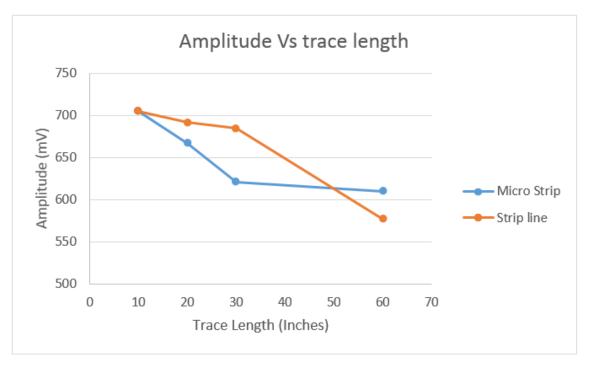

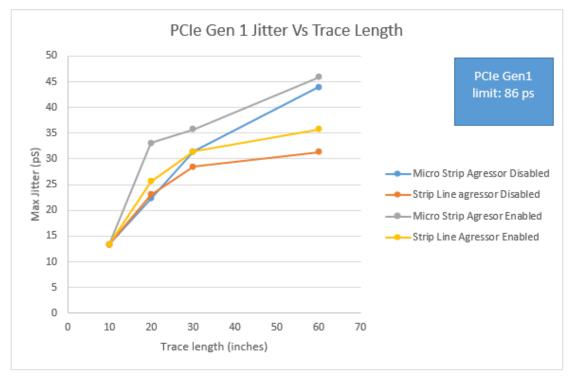

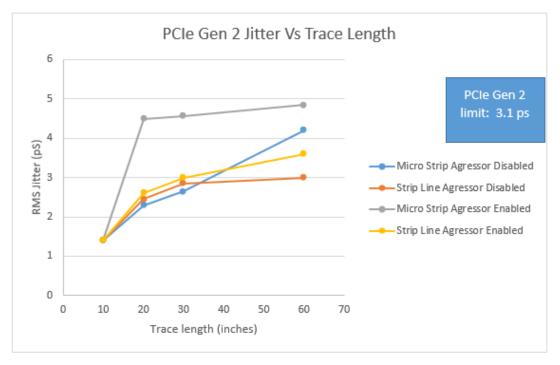

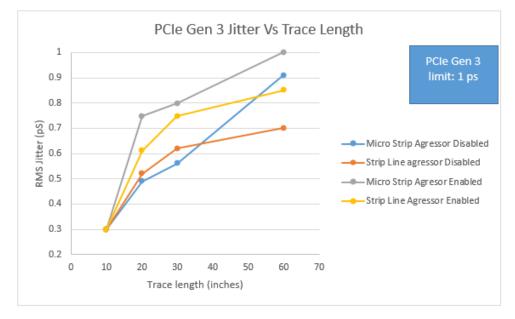

Figure 2.1 Aggressor Signals vs. HCSL Signals on the Long Trace Board on page 3 shows the input HCSL clock signal (Clk+, Clk–) coupled with the aggressor signal (Agg+, Agg–). The aggressor used is a 105 MHz differential noise at 3.3 V CMOS levels. Differential noise negates the noise immunity offered by differential signaling to noise, i.e., common mode noise. Both HCSL clock signal and aggressor signals are inputs to the long trace evaluation board. Figure 2.2 Slew Rate vs. Trace Length on page 3 through Figure 2.6 PCle Gen 3 Jitter (RMS) vs. Trace Length on page 5 show the impact of trace length and trace type on the HSCL clock signal driven by a push-pull buffer.

Figure 2.1. Aggressor Signals vs. HCSL Signals on the Long Trace Board

Figure 2.2. Slew Rate vs. Trace Length

Figure 2.3. Signal Amplitude vs. Trace Length

The signal amplitude and slew rate degrade at slower gradient on Strip Line traces as compared to Micro Strip traces. Refer to Figure 2.2 Slew Rate vs. Trace Length on page 3 and Figure 2.3 Signal Amplitude vs. Trace Length on page 4 for an illustration of this.

Figure 2.4. PCIe Gen 1 Peak-Peak Jitter vs. Trace Length

PCIe Gen 1 jitter degrades with trace length but is still within specifications. Strip Line traces perform better with trace length.

Figure 2.5. PCIe Gen 2 Jitter (RMS) vs. Trace Length

PCIe Gen 2 jitter degrades with trace length and can violate specifications. Strip Line traces perform better with trace length. For PCIe Gen 2 jitter compliance, care must be taken to minimize interference in order to enable driving long traces.

Figure 2.6. PCIe Gen 3 Jitter (RMS) vs. Trace Length

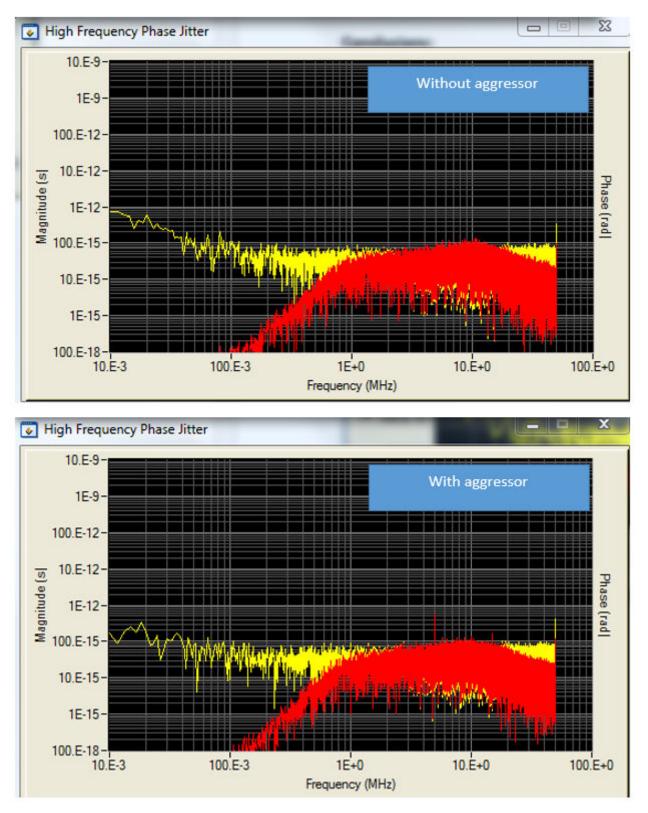

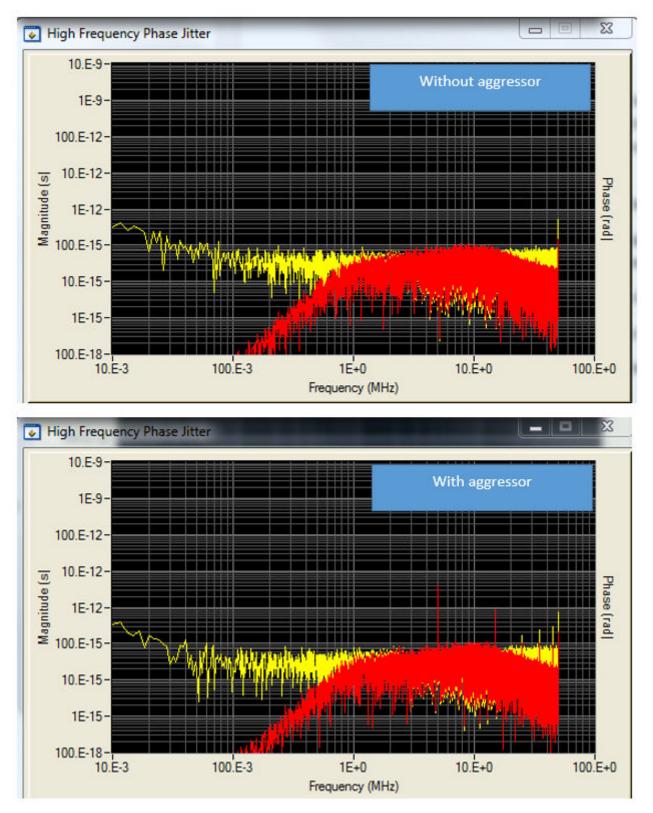

Figure 2.2 Slew Rate vs. Trace Length on page 3 through Figure 2.6 PCIe Gen 3 Jitter (RMS) vs. Trace Length on page 5 show that the Strip Line traces provide better PCIe performance, noise immunity and signal integrity over Micro Strip traces. The noise immunity of Strip Line traces are highlighted in the jitter transfer plots shown for PCIe Gen 1 phase jitter plots (See the figures below).

Figure 2.7. PCIe Gen 1 Jitter Transfer With and Without Aggressor Signal: Strip Line Trace

Figure 2.8. PCIe Gen 1 Jitter Transfer With and Without Aggressor Signal: Micro Strip Trace

AN951: Driving Long Traces on PCIe Backplanes for Simple Evaluation • Conclusion

#### 3. Conclusion

From the observations discussed, the key insights from the study are:

- 1. The signal amplitude and slew rate degrade at slower gradient on Strip Line traces as compared to Micro Strip traces.

- 2. This smaller gradient also helps reduce the gradient for PCIe jitter degradation, i.e., PCIe jitter performance on strip lines traces are better than on micro strip traces.

- 3. The strip line traces offer better immunity to differential noise, which in turn improves jitter performance, again pointing to better jitter performance on strip line traces as compared to micro strip traces.

Hence, it is preferable to use strip line traces when driving long traces on backplanes.

The long trace EVB can be used to make a similar analysis by emulating system design conditions to evaluate effect of long traces on PCIe performance.

## SKYWORKS

### **ClockBuilder Pro**

Customize Skyworks clock generators, jitter attenuators and network synchronizers with a single tool. With CBPro you can control evaluation boards, access documentation, request a custom part number, export for in-system programming and more!

www.skyworksinc.com/CBPro

C

**Portfolio** www.skyworksinc.com/ia/timing

www.skyworksinc.com/CBPro

Quality www.skyworksinc.com/quality

Support & Resources www.skyworksinc.com/support

#### Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5<sup>®</sup>, SkyOne<sup>®</sup>, SkyBlue<sup>™</sup>, Skyworks Green<sup>™</sup>, Clockbuilder<sup>®</sup>, DSPLL<sup>®</sup>, ISOmodem<sup>®</sup>, ProSLIC<sup>®</sup>, and SiPHY<sup>®</sup> are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.