# Si52254/Si52258 Data Sheet

# 4/8-Output PCIe Gen1/2/3/4/5 Clock Generator

The Si52258/54 are the industry's highest performance and lowest power automotive grade PCI Express clock generators for PCIe Gen1/2/3/4/5 common clock and/or SRIS applications. The Si52258 and Si52254 source eight and four 100 MHz PCIe differential clock outputs, respectively. All clock outputs are compliant to PCIe Gen1/2/3/4/5 common clock and separate reference clock architecture specifications.

Hardware control pins are available for enabling and disabling the outputs, as well as spread spectrum enable/disable for EMI reduction.

For more information about PCI Express, Skyworks' complete PCIe portfolio, application notes, and design tools, including the Skyworks PCIe Clock Jitter Tool for PCI Express compliance, please visit the Skyworks PCI Express Learning Center.

## Applications:

- · Infotainment

- ADAS ECU

- · Radar Sensors

- · LiDar Sensors

#### **KEY FEATURES**

- 8/4-outputs with internal termination

- PCIe Gen 1/2/3/4/5 compliant

- Automotive grade 2: -40 to +105 °C

- Internal 100  $\Omega$  or 85  $\Omega$  line matching

- · Excellent jitter performance

- 0.05 ps RMS (Gen3/4)

- 0.025 ps RMS (Gen5)

- Triangular spread spectrum for EMI reduction, down spread 0.25% or 0.5%

- Individual hardware control pins for Output Enable, Spread Spectrum Enable

- · Enable and Frequency Select

- 25 MHz crystal input or clock input

- 1.8-3.3 V power supply

- · Pb-free, RoHS-6 compliant

## 1. Features List

- 8/4-100 MHz HCSL outputs with internal termination

- PCIe Gen1/2/3/4/5 compliant

- Automotive grade 2: -40 to +105 °C

- Internal 100  $\Omega$  or 85  $\Omega$  line matching

- · Excellent jitter performance

- 0.05 ps RMS (Gen3/4)

- 0.025 ps RMS (Gen5)

- Triangular spread spectrum for EMI reduction, down spread 0.25% or 0.5%

- · Individual hardware control pins for Impedance Select, Output Enable, and Spread Spectrum Enable

- · Loss of Signal (LOS) output pin

- · 25 MHz crystal input or clock input

- 1.8-3.3 V power supply

- · Pb-free, RoHS-6 compliant

# 2. Ordering Guide

| Number of Outputs | Part Number     | Package Type           | Temperature               |

|-------------------|-----------------|------------------------|---------------------------|

| 8                 | Si52258A-D01AM  | 40-QFN                 | Automotive, –40 to 105 °C |

|                   | Si52258A-D01AMR | 40-QFN – Tape and Reel | Automotive, -40 to 105 °C |

| 4                 | Si52254A-D01AM  | 32-QFN                 | Automotive, -40 to 105 °C |

|                   | Si52254A-D01AMR | 32-QFN – Tape and Reel | Automotive, –40 to 105 °C |

# **Table of Contents**

| 1. | Features List                                    | . 2 |

|----|--------------------------------------------------|-----|

| 2. | Ordering Guide                                   | . 3 |

| 3. | Functional Description                           | . 5 |

|    | 3.1 Functional Block Diagram                     | . 5 |

|    | 3.2 Crystal Recommendations                      | . 5 |

|    | 3.3 HCSL Differential Output Terminations        | . 5 |

|    | 3.4 Output Enable/Disable                        | . 5 |

|    | 3.5 Spread Spectrum                              | . 5 |

|    | 3.6 Loss of Signal (LOS)                         | . 6 |

| 4. | Power Supply Filtering Recommendations           | . 7 |

| 5. | Electrical Specifications                        | . 8 |

| 6. | Pin Descriptions                                 | 14  |

|    | 6.1 Si52258A-D01AM Pin Descriptions (40-QFN)     | .14 |

|    | 6.2 Si5224A-D01AM Pin Descriptions (32-QFN)      | .18 |

| 7. | Package Outline                                  | 21  |

|    | 7.1 Si52258A-D01AM 6x6 mm 40-QFN Package Diagram | .21 |

|    | 7.2 Si52254A-D01AM 5x5 mm 32-QFN Package Diagram | .23 |

| 8. | PCB Land Pattern                                 | 25  |

|    | 8.1 Si52258A-D01AM 40-QFN Land Pattern           | .25 |

|    | 8.2 Si52254A-D01AM 32-QFN Land Pattern           | .27 |

| 9. | Top Marking                                      | 29  |

| 10 | D. Revision History.                             | 30  |

## 3. Functional Description

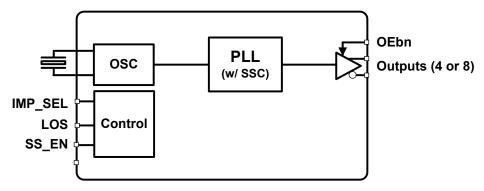

## 3.1 Functional Block Diagram

Figure 3.1. Si5225x Block Diagram

## 3.2 Crystal Recommendations

The Si52258/4 operates from a parallel resonance 25 MHz crystal operation requires external loading capacitors to match crystal capacitive loading requirements. Si52258/4 XA/XB inputs present 2.5 pf of stray capacitance.

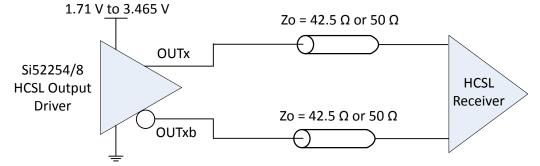

## 3.3 HCSL Differential Output Terminations

## **Termination for HCSL Outputs**

The Si52254/8 HCSL drivers feature integrated termination resistors to simplify interfacing to an HCSL receiver. The HCSL driver supports both 100  $\Omega$  and 85  $\Omega$  transmission line options, and can be selected using the IMP\_SEL hardware input pin.

Figure 3.2. HCSL Internal Termination Mode

## 3.4 Output Enable/Disable

An output enable pin provides a convenient method of disabling or enabling the output drivers. When the output enable pin is held high, all designated outputs will be disabled. When held low, the designated outputs will be enabled.

## 3.5 Spread Spectrum

To help reduce electromagnetic interference (EMI), the Si52254/8 supports spread spectrum modulation. Spread spectrum can be enabled by the hardware input pin.

## 3.6 Loss of Signal (LOS)

The LOS indicator is used to check for the presence of an input reference source (crystal). LOS will assert when the reference source frequency drops below approximately 10 MHz.

In the event that a reference source is not present, the associated LOS pin will assume a logic low (LOS = 0) state. When a reference source is present, the LOS pin will assume a logic high (LOS = 1) state.

The LOS output is active low, open drain, and requires an external pull-up resistor of 1 k $\Omega$  or greater.

# 4. Power Supply Filtering Recommendations

The Si52258/4 features internal LDOs on each power supply pin, providing excellent power supply noise rejection. As a guideline, each power supply pin should use a parallel combination of a 1  $\mu$ F bypass capacitor placed as close to the supply pin as possible.

## 5. Electrical Specifications

## **Table 5.1. Recommended Operating Conditions**

$(V_{DD} = V_{DDA} = V_{DD})_{DIG} = V_{DD})_{XTAL} = 1.8 \text{ V to } 3.3 \text{ V } +5\% -5\%, V_{DDO} = 1.8 \text{ V } \pm5\%, 2.5 \text{ V } \pm5\%, \text{ or } 3.3 \text{ V } \pm5\%, T_{A} = -40 \text{ to } 105 \text{ °C})$

| Parameter                           | Symbol                                                           | Test Condition | Min  | Тур | Max  | Units |

|-------------------------------------|------------------------------------------------------------------|----------------|------|-----|------|-------|

| Ambient Temperature                 | T <sub>A</sub>                                                   |                | -40  | 25  | 105  | °C    |

| Junction Temperature                | TJ <sub>MAX</sub>                                                |                | _    | _   | 125  | °C    |

| Core Supply Voltage <sup>1, 2</sup> | V <sub>DDA</sub> , V <sub>DD_DIG</sub> ,<br>V <sub>DD_xtal</sub> |                | 1.71 | _   | 3.46 | V     |

| Output Driver Supply Voltage        | $V_{DDO}$                                                        |                | 1.71 | _   | 3.46 | V     |

#### Note:

- 1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

- 2. All core voltages (VDD DIG, VDDA, VDD XTAL) must be connected to the same voltage.

#### Table 5.2. DC Characteristics

$(V_{DD} = V_{DDA} = V_{DD})_{DIG} = V_{DD})_{XTAL} = 1.8 \text{ V to } 3.3 \text{ V } +5\% -5\%, V_{DDO} = 1.8 \text{ V } \pm5\%, 2.5 \text{ V } \pm5\%, \text{ or } 3.3 \text{ V } \pm5\%, T_{A} = -40 \text{ to } 105 \text{ °C})$

| Parameter                            | Symbol            | Test Condition                     |  | Min | Тур | Max | Units |

|--------------------------------------|-------------------|------------------------------------|--|-----|-----|-----|-------|

| Core Supply Current                  | I <sub>DD</sub>   |                                    |  | _   | 26  | 40  | mA    |

| Output Buffer Supply Current         | I <sub>DDOx</sub> | HCSL Output <sup>1</sup> @ 100 MHz |  | _   | 20  | 22  | mA    |

| Tatal Davisa Disain attan?           |                   | 40-pin                             |  |     | 550 | 750 | mW    |

| Total Power Dissipation <sup>2</sup> | P <sub>d</sub>    | 32-pin                             |  | _   | 300 | 445 | mW    |

#### Notes:

- 1. Differential outputs terminated into a 100  $\Omega$  load at 3.3 V.

- 2. Total power dissipation calculated with all 100 MHz HCSL running at 3.3 V.

## Table 5.3. External Crystal Input Specification

$(V_{DD} = V_{DDA} = V_{DD})_{DIG} = V_{DD})_{XTAL} = 1.8 \text{ V to } 3.3 \text{ V } +5\% -5\%, V_{DDO} = 1.8 \text{ V } \pm5\%, 2.5 \text{ V } \pm5\%, \text{ or } 3.3 \text{ V } \pm5\%, T_{A} = -40 \text{ to } 105 \text{ °C})$

| Parameter           | Symbol            | Test Condition | Min  | Тур | Max | Units |

|---------------------|-------------------|----------------|------|-----|-----|-------|

| Crystal Frequency   | F <sub>xtal</sub> |                |      | 25  |     | MHz   |

| Crystal Drive Level | d <sub>L</sub>    |                | _    | _   | 250 | μW    |

| Input Capacitance   | C <sub>IN</sub>   |                | _    | 2.5 | _   | pF    |

| Input Voltage       | V <sub>XIN</sub>  |                | -0.3 | _   | 1.3 | V     |

#### Table 5.4. Differential Clock Output Specifications

$(V_{DD} = V_{DDA} = V_{DD})_{DIG} = V_{DD} \times TAL = 1.8 \text{ V to } 3.3 \text{ V } +5\% - 5\%, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 105 \text{ °C})$

| Parameter                        | Symbol                         | Test Condition |         | Min                    | Тур | Max                    | Units    |

|----------------------------------|--------------------------------|----------------|---------|------------------------|-----|------------------------|----------|

| Output Frequency                 | f <sub>OUT</sub>               |                |         |                        | 100 |                        | MHz      |

| Duty Cycle                       | DC                             |                |         | 48                     | _   | 52                     | %        |

| Output-Output Skew               | T <sub>SK</sub>                |                |         | _                      | _   | 80                     | ps       |

| Output Voltage Swing             | V <sub>SEPP</sub>              | HCSL           |         | 0.7                    | 0.8 | 0.9                    | $V_{PP}$ |

| Common Mode Voltage              | V <sub>CM</sub>                | HCSL           |         | 0.35                   | 0.4 | 0.45                   | V        |

| HCSL Edge Rate                   | Edgr                           | Notes 1, 2, 3  |         | 1                      | _   | 4.5                    | V/ns     |

| HCSL Delta Tr                    | D <sub>tr</sub>                | Notes 2, 4, 5  |         | _                      | _   | 155                    | ps       |

| HCSL Delta Tf                    | D <sub>tf</sub>                | Notes 2        | 2, 4, 5 | _                      | _   | 155                    | ps       |

| HCSL Vcross Abs                  | V <sub>xa</sub>                | Notes 6,       | 7, 2, 4 | 250                    | _   | 550                    | mV       |

| HCSL Delta Vcross                | D <sub>vcrs</sub>              | Notes 2, 4, 8  |         | _                      | _   | 140                    | mV       |

| HCSL Vovs                        | V <sub>ovs</sub>               | Notes 2, 4, 9  |         | _                      | _   | V <sub>HIGH</sub> +300 | mV       |

| HCSL Vuds                        | V <sub>uds</sub>               | Notes 2, 4, 10 |         | _                      | _   | V <sub>LOW</sub> -300  | mV       |

| HCSL Vrng                        | V <sub>rng</sub>               | Notes 2, 4     |         | V <sub>HIGH</sub> -200 | _   | V <sub>LOW</sub> +200  | mV       |

| Rise and Fall Times (20% to 80%) | t <sub>R</sub> /t <sub>F</sub> | HCSL           |         | _                      | _   | 420                    | ps       |

- 1. Measure taken from differential waveform on a component test board. The edge (slew) rate is measured from -150 mV to +150 mV on the differential waveform. Scope is set to average because the scope sample clock is making most of the dynamic wiggles along the clock edge Only valid for Rising clock and Falling Clock#. Signal must be monotonic through the Vol to Voh region for Trise and Tfall.

- 2. Applies to a 2 pf load with both internal or external 50  $\Omega$  or 42.5  $\Omega$  Rp.

- 3. Measurement taken from differential waveform.

- 4. Measurement taken from Single Ended waveform.

- 5. Measured with oscilloscope, averaging off, using min max statistics. Variation is the delta between min and max.

- 6. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLK#.

- 7. This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

- 8. ΔVcross is defined as the total variation of all crossing voltages of Rising CLOCK and Falling CLOCK#. This is the maximum allowed variance in Vcross for any particular system.

- 9. Overshoot is defined as the absolute value of the maximum voltage.

- 10. Undershoot is defined as the absolute value of the minimum voltage.

#### **Table 5.5. Performance Characteristics**

$(V_{DD} = V_{DDA} = V_{DD\_DIG} = V_{DD\_XTAL} = 1.8 \text{ V to } 3.3 \text{ V } +5\% / -5\%, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 105 \text{ °C})$

| Parameter                            | Symbol              | Test Condition                             | Min | Тур  | Max | Units |

|--------------------------------------|---------------------|--------------------------------------------|-----|------|-----|-------|

| Power Ramp                           | t <sub>VDD</sub>    | 0 V to V <sub>DDmin</sub>                  | 0.1 | _    | 10  | ms    |

| Clock Stabilization from Power-up    | t <sub>STABLE</sub> | Time for clock outputs to appear after POR | _   | 15   | 25  | ms    |

| 0.5% Down Spread Frequency Deviation | SSDEV               |                                            | 0.4 | 0.45 | 0.5 | %     |

| Spread Spectrum Modulation Rate      | SSDEV               |                                            | 30  | 31.5 | 33  | kHz   |

<sup>1.</sup> Default value is ~31.5 kHz.

Table 5.6. PCI-Express Clock Outputs (100 MHz HCSL)

$(V_{DD} = V_{DDA} = V_{DD\_DIG} = V_{DD\_XTAL} = 1.8 \text{ V to } 3.3 \text{ V } +5\% / -5\%, V_{DDO} = 1.8 \text{ V } \pm 5\%, 2.5 \text{ V } \pm 5\%, \text{ or } 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 105 \text{ °C})$

| Parameter                      | Test Condition                                                  | SSC On/Off | Тур   | Max   | Units  |

|--------------------------------|-----------------------------------------------------------------|------------|-------|-------|--------|

|                                | Includes PLL BW 1.5–22 MHz,                                     | Off        | 11    | 19    | ps RMS |

| PCle Gen 1.1                   | Peaking = 3 dB, Td = 10 ns,                                     | 0          | 00    |       | DMC    |

|                                | Ftrk = 1.5 MHz with BER = 1E-12 $^{1}$                          | On         | 22    | 30    | ps RMS |

|                                | Includes PLL BW 5MHz and 8–16 MHz,                              | Off        | 0.02  | 0.026 | ps RMS |

|                                | Jitter Peaking = 0.01–1 dB and 3 dB,                            | 0          | 0.40  | 0.04  | D140   |

| PCle Gen 2.1                   | Td = 12 ns, Low Band, $F < 1.5 \text{ MHz}^1$                   | On         | 0.12  | 0.21  | ps RMS |

| Pole Gen 2.1                   | Includes PLL BW 5 MHz and 8–16 MHz,                             | Off        | 0.2   | 0.31  | ps RMS |

|                                | Jitter Peaking = 0.01–1 dB and 3 dB,                            | 0          | 0.0   | 4.05  | DMC    |

|                                | Td = 12 ns, High Band, 1.5 MHz < F < Nyquist <sup>1</sup>       | On         | 0.8   | 1.35  | ps RMS |

| DOI: 0 0 0 0                   | Includes PLL BW 2–4 MHz and 5 MHz, Peaking =                    | Off        | 0.06  | 0.1   | ps RMS |

| PCIe Gen 3.0 Com-<br>mon Clock | 0.01–2 dB and 1 dB,                                             | On         | 0.26  | 0.38  | ps RMS |

|                                | Td = 12 ns, CDR = 10 MHz <sup>1, 2</sup>                        |            |       |       | P      |

|                                | Includes PLL BW 4 MHz                                           |            |       |       |        |

| PCIe Gen3.0 SRIS               | Peaking = 2 dB and 1dB, Td = 12 ns                              | On         | 0.35  | 0.37  | ps RMS |

|                                | CDR = 10 MHz <sup>1, 2</sup>                                    |            |       |       |        |

| PCIe Gen 4.0 Com-              | Includes PLL BW 2–4 MHz and 5 MHz, Peaking = 0.01–2 dB and 1dB, | Off        | 0.05  | 0.1   | ps RMS |

| mon Clock                      | Td = 12 ns, CDR = 10 MHz <sup>1, 2</sup>                        | On         | 0.26  | 0.38  | ps RMS |

|                                |                                                                 |            |       |       |        |

|                                | Includes PLL BW 4 MHz                                           |            |       |       |        |

| PCIe Gen4.0 SRIS               | Peaking = 2 dB and 1 dB, Td = 12 ns                             | On         | 0.31  | 0.38  | ps RMS |

|                                | CDR = 10 MHz <sup>1, 2</sup>                                    |            |       |       |        |

| PCIe Gen5.0 Com-               |                                                                 | Off        | 0.025 | 0.04  | ps RMS |

| mon Clock                      |                                                                 | On         | 0.1   | 0.15  | ps RMS |

| PCIe Gen5.0 SRIS               |                                                                 | On         | 0.08  | 0.1   | ps RMS |

<sup>1.</sup> All output clocks 100 MHz HCSL format. Jitter data taken from Clock Jitter Tool v.1.3.

<sup>2.</sup> Excludes oscilloscope sampling noise.

**Table 5.7. Thermal Characteristics**

| Parameter                               | Symbol          | Test Condition <sup>1</sup> | Value | Units |

|-----------------------------------------|-----------------|-----------------------------|-------|-------|

| Si52258 — 40 QFN                        |                 |                             |       |       |

|                                         |                 | Still Air                   | 23.1  |       |

| Thermal Resistance, Junction to Ambient | θ <sub>JA</sub> | Air Flow 1 m/s              | 17.5  |       |

|                                         |                 | Air Flow 2 m/s              | 16.5  | 0000  |

| Thermal Resistance, Junction to Case    | θ <sub>JC</sub> |                             | 13.4  | °C/W  |

| Thermal Resistance, Junction to Board   | $\theta_{JB}$   |                             | 8.7   |       |

|                                         | ΨЈВ             | Still Air                   | 8.4   |       |

| Si52254 — 32 QFN                        |                 |                             |       |       |

|                                         |                 | Still Air                   | 28.4  |       |

| Thermal Resistance, Junction to Ambient | θ <sub>JA</sub> | Air Flow 1 m/s              | 24    |       |

|                                         |                 | Air Flow 2 m/s              | 23    |       |

| Thermal Resistance, Junction to Case    | θ <sub>JC</sub> |                             | 15.9  | °C/W  |

|                                         | $\theta_{JB}$   |                             | 11.5  |       |

| Thermal Resistance, Junction to Board   | OJB             |                             |       |       |

<sup>1.</sup> Based on JEDEC standard 4-layer PCB.

Table 5.8. Absolute Maximum Ratings<sup>1,2,3</sup>

| Parameter                                       | Symbol              | Test Condition | Value       | Units  |

|-------------------------------------------------|---------------------|----------------|-------------|--------|

| Storage Temperature Range                       | T <sub>STG</sub>    |                | -55 to +150 | °C     |

|                                                 | V <sub>DD</sub>     |                | -0.5 to 3.8 | V      |

| DC Cumply Voltage                               | $V_{\mathrm{DDA}}$  |                | -0.5 to 3.8 | V      |

| DC Supply Voltage                               | VDD <sub>xtal</sub> |                | -0.5 to 3.8 | V      |

|                                                 | V <sub>DDO</sub>    |                | -0.5 to 3.8 | V      |

| Input Voltage Range                             | VI                  | XIN/XOUT       | -0.3 to 1.3 | V      |

| Latch-up Tolerance                              | LU                  |                | JESD78 Com  | pliant |

| ESD Tolerance                                   | НВМ                 | 100 pF, 1.5 kΩ | 2.0         | kV     |

| Junction Temperature                            | T <sub>JCT</sub>    |                | -55 to 125  | °C     |

| Soldering Temperature                           | T <sub>PEAK</sub>   |                | 260         | °C     |

| Soldering Temperature Time at T <sub>PEAK</sub> | T <sub>P</sub>      |                | 20 to 40    | sec    |

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. For more packaging information, go to https://www.skyworksinc.com/product\_certificate.aspx.

- 3. The device is compliant with JEDEC J-STD-020.

# 6. Pin Descriptions

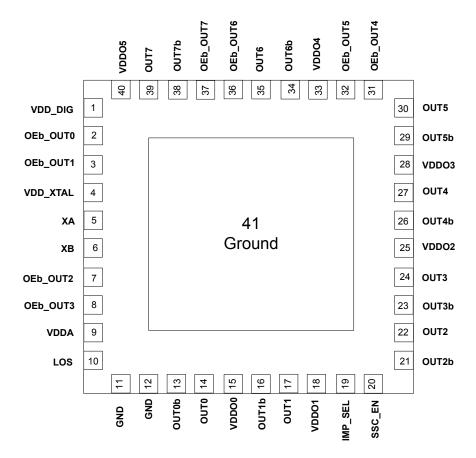

## 6.1 Si52258A-D01AM Pin Descriptions (40-QFN)

Figure 6.1. 40-QFN

Table 6.1. Si52258A-D01AM Pin Descriptions (40-QFN)

| Pin Number | Pin Name | Pin Type                      | Function                                                                                                                                                                                                                                                                                                                                                                              |  |                             |

|------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------|

| 1          | VDD_DIG  | Р                             | Voltage supply for digital functions. Connect to 1.8–3.3 V. Part of internal core VDD voltage. Must be connected to same voltage as VDDA and VDD_XTAL. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.                                                                                                                                       |  |                             |

|            |          |                               | Output enable pin for OUT1.                                                                                                                                                                                                                                                                                                                                                           |  |                             |

| 2          | OEb_OUT0 | o_OUT0 I Low = output enabled | Low = output enabled                                                                                                                                                                                                                                                                                                                                                                  |  |                             |

|            |          |                               | High = output disabled                                                                                                                                                                                                                                                                                                                                                                |  |                             |

|            |          |                               | Output enable pin for OUT1.                                                                                                                                                                                                                                                                                                                                                           |  |                             |

| 3          | OEb_OUT1 | 1                             | Low = output enabled                                                                                                                                                                                                                                                                                                                                                                  |  |                             |

|            |          |                               | High = output disabled                                                                                                                                                                                                                                                                                                                                                                |  |                             |

| 4          | VDD_XTAL | Р                             | Voltage supply for crystal oscillator. Connect to 1.8–3.3 V. Part of internal core VDD voltage. Must be connected to same voltage as VDDA and VDD_DIG. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.                                                                                                                                       |  |                             |

| 5          | XA       | l                             | Connect to 25 MHz input crystal. Refer to Section 5. Electrical Specifica-                                                                                                                                                                                                                                                                                                            |  |                             |

| 6          | XB       | 0                             | tions for recommended crystal specifications.                                                                                                                                                                                                                                                                                                                                         |  |                             |

|            |          |                               |                                                                                                                                                                                                                                                                                                                                                                                       |  | Output enable pin for OUT2. |

| 7          | OEb_OUT2 | 1                             | Low = output enabled                                                                                                                                                                                                                                                                                                                                                                  |  |                             |

|            |          |                               | High = output disabled                                                                                                                                                                                                                                                                                                                                                                |  |                             |

|            |          |                               | Output enable pin for OUT3.                                                                                                                                                                                                                                                                                                                                                           |  |                             |

| 8          | OEb_OUT3 | I                             | Low = output enabled                                                                                                                                                                                                                                                                                                                                                                  |  |                             |

|            |          |                               | High = output disabled                                                                                                                                                                                                                                                                                                                                                                |  |                             |

|            |          |                               | Core Supply Voltage. Connect to 1.8–3.3 V.                                                                                                                                                                                                                                                                                                                                            |  |                             |

| 9          | VDDA     | Р                             | Must be connected to same voltage as VDD_DIG and VDD_XTAL.                                                                                                                                                                                                                                                                                                                            |  |                             |

|            |          |                               | Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.                                                                                                                                                                                                                                                                                              |  |                             |

| 10         | LOS      | 0                             | The LOS status pin indicates whether the reference input has dropped below approximately 10 MHz. LOS is active low, open drain output and requires an external pull-up resistor of 1 to 10 k $\Omega$ for proper operation. If LOS is not required, this pin can be left unconnected.  0 = reference input has dropped below approx. 10 MHz  1 = reference input is present (>10 MHz) |  |                             |

| 11         | GND      | _                             | Connect this pin to ground.                                                                                                                                                                                                                                                                                                                                                           |  |                             |

| 12         | GND      | _                             | Connect this pin to ground.                                                                                                                                                                                                                                                                                                                                                           |  |                             |

| 13         | OUT0b    | 0                             | Output Clock                                                                                                                                                                                                                                                                                                                                                                          |  |                             |

| 14         | OUT0     | 0                             | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                                                                                                                                |  |                             |

| Pin Number | Pin Name | Pin Type | Function                                                                                                                                                                                                                                                                         |

|------------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT0                                                                                                                                                                                                                                              |

| 15         | VDD00    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 16         | OUT1b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 17         | OUT1     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT1                                                                                                                                                                                                                                              |

| 18         | VDDO1    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 40         | IMP OF   |          | Impedance select pin for output drivers. IMP_SEL pin is sampled at power-up only.                                                                                                                                                                                                |

| 19         | IMP_SEL  | I        | Low = 100 Ω                                                                                                                                                                                                                                                                      |

|            |          |          | High = $85 \Omega$                                                                                                                                                                                                                                                               |

|            |          |          | Spread spectrum enable pin.                                                                                                                                                                                                                                                      |

| 20         | SSC_EN   | SSC_EN I | Low = spread OFF                                                                                                                                                                                                                                                                 |

|            |          |          | High = spread ON (-0.5%)                                                                                                                                                                                                                                                         |

| 21         | OUT2b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 22         | OUT2     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

| 23         | OUT3b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 24         | ОИТЗ     | О        | Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                                                |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT2 and OUT3                                                                                                                                                                                                                                     |

| 25         | VDDO2    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 26         | OUT4b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 27         | OUT4     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT4 and OUT5                                                                                                                                                                                                                                     |

| 28         | VDDO3    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 29         | OUT5b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 30         | OUT5     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

| Pin Number | Pin Name | Pin Type | Function                                                                                                                                                                                                                                                                         |

|------------|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |          | Output enable pin for OUT4.                                                                                                                                                                                                                                                      |

| 31         | OEb_OUT4 | 1        | Low = output enabled                                                                                                                                                                                                                                                             |

|            |          |          | High = output disabled                                                                                                                                                                                                                                                           |

|            |          |          | Output enable pin for OUT5.                                                                                                                                                                                                                                                      |

| 32         | OEb_OUT5 | 1        | Low = output enabled                                                                                                                                                                                                                                                             |

|            |          |          | High = output disabled                                                                                                                                                                                                                                                           |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT6                                                                                                                                                                                                                                              |

| 33         | VDDO4    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 34         | OUT6b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 35         | OUT6     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

|            |          |          | Output enable pin for OUT6.                                                                                                                                                                                                                                                      |

| 36         | OEb_OUT6 | 1        | Low = output enabled                                                                                                                                                                                                                                                             |

|            |          |          | High = output disabled                                                                                                                                                                                                                                                           |

|            |          |          | Output enable pin for OUT7.                                                                                                                                                                                                                                                      |

| 37         | OEb_OUT7 | 1        | Low = output enabled                                                                                                                                                                                                                                                             |

|            |          |          | High = output disabled                                                                                                                                                                                                                                                           |

| 38         | OUT7b    | 0        | Output Clock                                                                                                                                                                                                                                                                     |

| 39         | OUT7     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT7                                                                                                                                                                                                                                              |

| 40         | VDDO5    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

|            |          |          | Ground Pad                                                                                                                                                                                                                                                                       |

| 41         | GND PAD  | Р        | This pad provides electrical and thermal connection to ground and must be connected for proper operation.                                                                                                                                                                        |

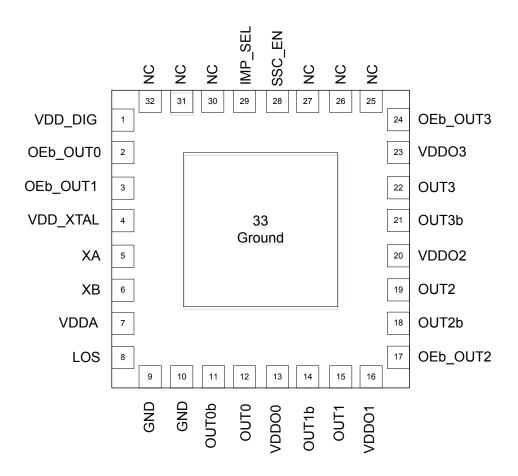

## 6.2 Si5224A-D01AM Pin Descriptions (32-QFN)

Figure 6.2. 32-QFN

Table 6.2. Si5224A-D01AM Pin Descriptions, (32-QFN)

| Pin Number | Pin Name | Pin Type | Function                                                                                                                                                                                                                                         |

|------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDD_DIG  | Р        | Voltage supply for digital functions. Connect to 1.8–3.3 V. Part of internal core VDD voltage. Must be connected to same voltage as VDDA and VDD_XTAL. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.  |

| 2          | OEb_OUT0 | I        | Output enable pin for OUT0.  Low = output enabled  High = output disabled                                                                                                                                                                        |

| 3          | OEb_OUT1 | I        | Output enable pin for OUT1.  Low = output enabled  High = output disabled                                                                                                                                                                        |

| 4          | VDD_XTAL | Р        | Voltage supply for crystal oscillator. Connect to 1.8–3.3 V. Part of internal core VDD voltage. Must be connected to same voltage as VDDA and VDD_DIG." Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 5          | XA       | I        | Refer to Section 5. Electrical Specifications for recommended crystal speci-                                                                                                                                                                     |

| 6          | ХВ       | 0        | fications.                                                                                                                                                                                                                                       |

| Pin Number | Pin Name | Pin Type | Function                                                                                                                                                                                                                                                                              |

|------------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |          | Core Supply Voltage. Connect to 1.8–3.3 V.                                                                                                                                                                                                                                            |

| 7          |          | Р        | See the Si5332-AM1/2/3 Family Reference Manual for power supply filtering recommendations.                                                                                                                                                                                            |

| 1          | VDDA     |          | Must be connected to same voltage as VDD_DIG and VDD_XTAL.                                                                                                                                                                                                                            |

|            |          |          | Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.                                                                                                                                                                                              |

| 8          | 8 LOS    |          | The LOS status pin indicates whether the reference input has dropped below approximately 10 MHz. LOS is active low, open drain output and requires an external pull-up resistor of 1 to 10 k $\Omega$ for proper operation. If LOS is not required, this pin can be left unconnected. |

|            |          |          | 0 = reference input has dropped below approx. 10 MHz                                                                                                                                                                                                                                  |

|            |          |          | 1 = reference input is present (>10 MHz)                                                                                                                                                                                                                                              |

| 9          | GND      | Р        | Connect these pins to ground.                                                                                                                                                                                                                                                         |

| 10         | GND      | Р        | Connect triese pins to ground.                                                                                                                                                                                                                                                        |

| 11         | OUT0b    | 0        | Output Clock                                                                                                                                                                                                                                                                          |

| 12         | OUT0     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                                |

|            | VDDO0    | Р        | Supply Voltage (1.8–3.3 V) for OUT0                                                                                                                                                                                                                                                   |

| 13         |          |          | See the Si5332-AM1/2/3 Family Reference Manual for power supply filtering recommendations.  Leave VDDOx pins of unused output drivers unconnected. An alternate                                                                                                                       |

|            |          |          | option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.                                                                          |

| 14         | OUT1b    | 0        | Output Clock                                                                                                                                                                                                                                                                          |

| 15         | OUT1     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                                |

|            |          |          | Supply Voltage (1.8–3.3 V) for OUT1                                                                                                                                                                                                                                                   |

| 16         | VDDO1    | Р        | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations.      |

|            | OEb_OUT2 | I        | Output enable pin for OUT2.                                                                                                                                                                                                                                                           |

| 17         |          |          | Low = output enabled                                                                                                                                                                                                                                                                  |

|            |          |          | High = output disabled                                                                                                                                                                                                                                                                |

| 18         | OUT2b    | 0        | Output Clock                                                                                                                                                                                                                                                                          |

| 19         | OUT2     | 0        | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                                |

| Pin Number | Pin Name | Pin Type     | Function                                                                                                                                                                                                                                                                         |

|------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          |              | Supply Voltage (1.8–3.3 V) for OUT2                                                                                                                                                                                                                                              |

| 20         | VDDO2    | Р            | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

| 21         | OUT3b    | 0            | Output Clock                                                                                                                                                                                                                                                                     |

| 22         | OUT3     | 0            | 100 MHz HCSL output. Termination recommendations are provided in 3.3 HCSL Differential Output Terminations. Unused outputs should be left unconnected.                                                                                                                           |

|            |          |              | Supply Voltage (1.8–3.3 V) for OUT3                                                                                                                                                                                                                                              |

| 23         | VDDO3    | Р            | Leave VDDOx pins of unused output drivers unconnected. An alternate option is to connect the VDDOx pin to a power supply and disable the output driver to minimize current consumption. Refer to 4. Power Supply Filtering Recommendations for bypass capacitor recommendations. |

|            |          |              | Output enable pin for OUT3.                                                                                                                                                                                                                                                      |

| 24         | OEb_OUT3 | 1            | Low = output enabled                                                                                                                                                                                                                                                             |

|            |          |              | High = output disabled                                                                                                                                                                                                                                                           |

| 25         | NC       | _            |                                                                                                                                                                                                                                                                                  |

| 26         | NC       | _            | Do not connect these pins to anything.                                                                                                                                                                                                                                           |

| 27         | NC       | <del>_</del> |                                                                                                                                                                                                                                                                                  |

|            |          |              | Spread spectrum enable pin.                                                                                                                                                                                                                                                      |

| 28         | SSC_EN   | 1            | Low = spread OFF                                                                                                                                                                                                                                                                 |

|            |          |              | High = spread ON (-0.5%)                                                                                                                                                                                                                                                         |

|            |          |              | Impedance select pin for output drivers. IMP_SEL pin is sampled at power-up only.                                                                                                                                                                                                |

| 29         | IMP_SEL  | I            | Low = 100 Ω                                                                                                                                                                                                                                                                      |

|            |          |              | High = 85 Ω                                                                                                                                                                                                                                                                      |

| 30         | NC       | _            |                                                                                                                                                                                                                                                                                  |

| 31         | NC       | _            | Do not connect these pins to anything.                                                                                                                                                                                                                                           |

| 32         | NC       | _            |                                                                                                                                                                                                                                                                                  |

|            |          |              | Ground Pad                                                                                                                                                                                                                                                                       |

| 33         | GND PAD  | Р            | This pad provides electrical and thermal connection to ground and must be connected for proper operation.                                                                                                                                                                        |

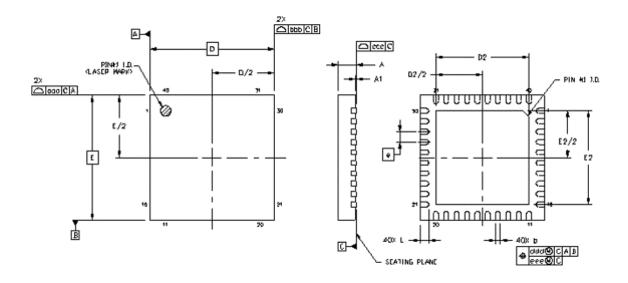

# 7. Package Outline

# 7.1 Si52258A-D01AM 6x6 mm 40-QFN Package Diagram

The figure below illustrates the package details for the Si52258A-D01AM in 40-QFN. The table below lists the values for the dimensions shown in the illustration.

Figure 7.1. 40-Pin Quad Flat No-Lead (QFN)

Table 7.1. Package Dimensions

| Dimension | Min      | Nom      | Max  |

|-----------|----------|----------|------|

| A         | 0.80     | 0.85     | 0.90 |

| A1        | 0.00     | 0.02     | 0.05 |

| b         | 0.18     | 0.25     | 0.30 |

| D         |          | 6.00 BSC |      |

| D2        | 4.35     | 4.50     | 4.65 |

| е         | 0.50 BSC |          |      |

| E         | 6.00 BSC |          |      |

| E2        | 4.35     | 4.50     | 4.65 |

| L         | 0.30     | 0.40     | 0.50 |

| aaa       | _        | _        | 0.15 |

| bbb       | _        | _        | 0.15 |

| ccc       | _        | _        | 0.08 |

| ddd       | _        | _        | 0.10 |

| eee       |          |          | 0.05 |

Dimension Min Nom Max

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-220.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

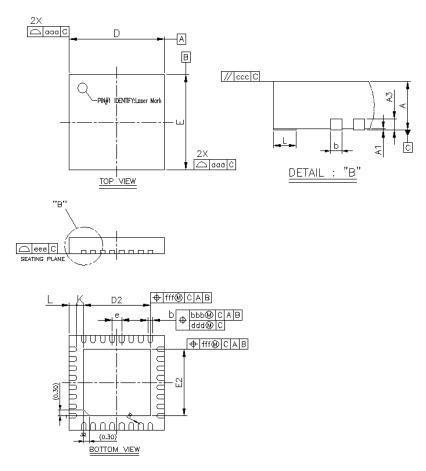

## 7.2 Si52254A-D01AM 5x5 mm 32-QFN Package Diagram

The figure below illustrates the package details for the Si52254A-D01AM 32-QFN option. The table below lists the values for the dimensions shown in the illustration.

Figure 7.2. 32-Pin Quad Flat No-Lead (QFN)

Table 7.2. Package Dimensions

| Dimension | MIN  | NOM      | MAX  |

|-----------|------|----------|------|

| A         | 0.80 | 0.85     | 0.90 |

| A1        | 0.00 | 0.02     | 0.05 |

| A3        |      | 0.20 REF |      |

| b         | 0.18 | 0.25     | 0.30 |

| D/E       | 4.90 | 5.00     | 5.10 |

| D2/E2     | 3.40 | 3.50     | 3.60 |

| е         |      | 0.50 BSC |      |

| L         | 0.30 | 0.40     | 0.50 |

| К         | 0.20 |          |      |

| R         | 0.09 |          | 0.14 |

| aaa       | 0.15 |          |      |

| bbb       | 0.10 |          |      |

| ccc       | 0.10 |          |      |

| Dimension | MIN | NOM  | MAX |

|-----------|-----|------|-----|

| ddd       |     | 0.05 |     |

| eee       |     | 0.08 |     |

| fff       | fff |      |     |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-220, Variation VKKD-4.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 8. PCB Land Pattern

## 8.1 Si52258A-D01AM 40-QFN Land Pattern

Figure 8.1. 40-QFN Land Pattern

Table 8.1. PCB Land Pattern Dimensions

| Dimension | mm       |

|-----------|----------|

| C1        | 5.90     |

| C2        | 5.90     |

| е         | 0.50 BSC |

| X1        | 0.30     |

| Y1        | 0.85     |

| X2        | 4.65     |

| Y2        | 4.65     |

Dimension mm

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

## Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size can be 1:1 for all perimeter pads.

- 4. A 3×3 array of 0.85 mm square openings on a 1.00 mm pitch can be used for the center ground pad.

## **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

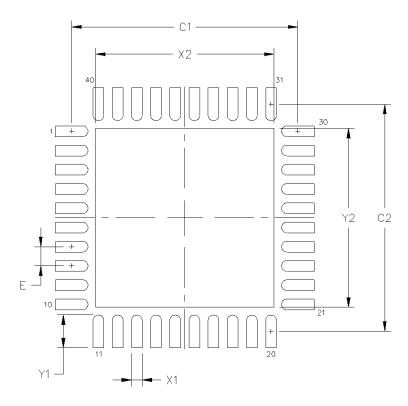

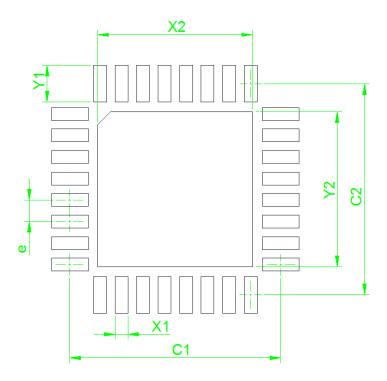

## 8.2 Si52254A-D01AM 32-QFN Land Pattern

The figure below illustrates the PCB land pattern details for Si52254A-D01AM in 32-QFN package. The table below lists the values for the dimensions shown in the illustration.

Figure 8.2. 32-QFN Land Pattern

Table 8.2. PCB Land Pattern Dimensions

| Dimension | mm       |

|-----------|----------|

| C1        | 4.90     |

| C2        | 4.90     |

| е         | 0.50 BSC |

| X1        | 0.30     |

| Y1        | 0.85     |

| X2        | 3.60     |

| Y2        | 3.60     |

Dimension mm

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

## Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size can be 1:1 for all perimeter pads.

- 4. A 3×3 array of 0.85 mm square openings on a 1.00 mm pitch can be used for the center ground pad.

## **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 9. Top Marking

Figure 9.1. Top Marking

**Table 9.1. Top Marking Explanation**

| Line | Characters         | Description                                                           |

|------|--------------------|-----------------------------------------------------------------------|

| 1    | Si52258<br>Si52254 | Base part number                                                      |

|      |                    | A = Grade                                                             |

| 2    | AR01A              | R = Product revision (reference ordering section for latest revision) |

| 2    | ARUTA              | 01 = Product identification, single input                             |

|      |                    | A = Automotive temperature grade. Package (QFN)                       |

| 3    | ТТТТТТ             | Manufacturing trace code.                                             |

| 4    | YYWW               | Year (YY) and work week (WW) of package assembly                      |

## 10. Revision History

## Revision 1.0

January, 2021

- Updated Table 5.4 Differential Clock Output Specifications on page 9.

- Updated Table 6.1 Si52258A-D01AM Pin Descriptions (40-QFN) on page 15.

- Removed "Default low" from hardware input pin function descriptions.

- Updated Table 6.2 Si5224A-D01AM Pin Descriptions, (32-QFN) on page 18.

- Removed "Default low" from hardware input pin function descriptions.

- · Updated 9. Top Marking.

- Updated Typ/Max performance specs in Table 5.6 PCI-Express Clock Outputs (100 MHz HCSL) on page 11.

## Revision 0.7

September, 2019

· Initial release.

www.skyworksinc.com/CBPro

**Quality** www.skyworksinc.com/quality

**Support & Resources** www.skyworksinc.com/support

## Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.