# Si51214 Data Sheet

## Two Output Factory Programmable Clock Generator

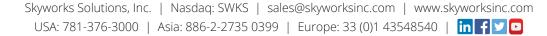

The factory programmable Si51214 is the industry's lowest power, smallest footprint and frequency flexible programmable clock generator targeting low power, low cost and high volume consumer and embedded applications. The device operates from a single crystal or an external clock source and generates 1 to 2 outputs up to 133 MHz. The device is factory programmed to provide customized output frequencies and control input such as frequency select, spread spectrum on, power down and output enable. Center spread spectrum can also be programmed to reduce EMI to meet board level system requirements.

#### Applications

- Crystal/XO replacement

- EMI reduction

- · Portable devices

- · Digital still camera

- IP phone

- Smart meter

#### KEY FEATURES

- Generates up to 2 CMOS clock outputs from 3 to 133 MHz

- Accepts crystal or reference clock input

- 3 to 165 MHz reference clock input

8 to 48 MHz crystal input

- Programmable FSEL, SSONb, PD, and OE input functions

Si51214 Data Sheet • Feature List

## 1. Feature List

The Si51214 highlighted features are listed below.

- · Generates up to 2 CMOS clock outputs from 3 to 133 MHz

- Accepts crystal or reference clock input

- 3 to 165 MHz reference clock input

- 8 to 48 MHz crystal input

- · Programmable FSEL, SSONb, PD, and OE input functions

- · Low power dissipation

- 1.8 V voltage supply range

- ±0.25%, ±0.5% or ±1% spread spectrum (center spread)

- · Low cycle-cycle jitter

- Ultra small 6-pin TDFN package (1.2 mm x 1.4 mm)

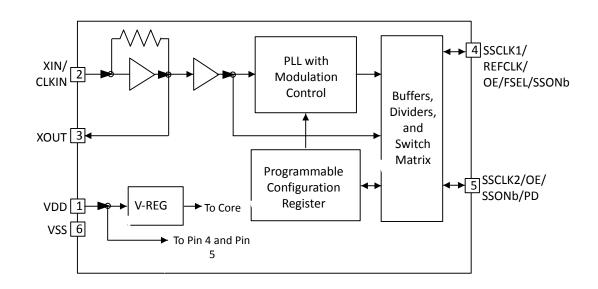

## 2. Ordering Guide

## Table 2.1. Si51214 Ordering Guide

## **Table of Contents**

| 1. | Feature List                              | . 2 |

|----|-------------------------------------------|-----|

| 2. | Ordering Guide                            | . 3 |

| 3. | Design Considerations                     | . 5 |

|    | 3.1 Typical Application Schematic         | . 5 |

|    | 3.2 Comments and Recommendations          | . 5 |

| 4. | Electrical Specifications                 | . 6 |

| 5. | Functional Description                    | . 8 |

|    | 5.1 Input Frequency Range                 | . 8 |

|    | 5.2 Input Reference Power On Sequence     | . 8 |

|    | 5.3 Output Frequency Range and Outputs    | . 8 |

|    | 5.4 Programmable Spread Percent (%)       | . 8 |

|    | 5.5 SSONb or Frequency Select (FSEL).     | . 8 |

|    | 5.6 Power Down (PD) or Output Enable (OE) | . 8 |

| 6. | Pin Description                           | . 9 |

| 7. | Package Outline                           | 10  |

| 8. | PCB Land Pattern                          | 12  |

| 9. | Revision History                          | 14  |

|    | 9.1 Revision 1.1                          | .14 |

|    | 9.2 Revision 1.0                          | .14 |

Si51214 Data Sheet • Design Considerations

## 3. Design Considerations

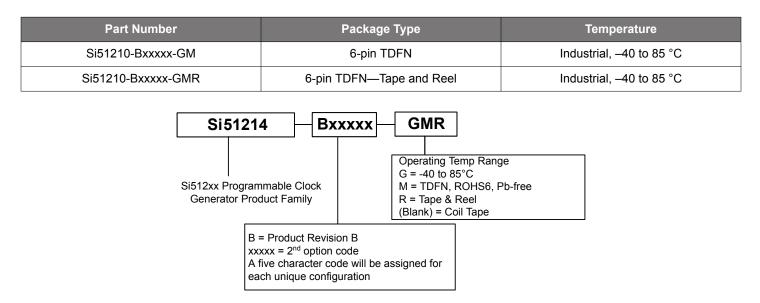

#### 3.1 Typical Application Schematic

#### 3.2 Comments and Recommendations

**Decoupling Capacitor**: A decoupling capacitor of 0.1  $\mu$ F must be used between VDD and VSS on pin 1. Place the capacitor on the component side of the PCB as close to the VDD pin as possible. The PCB trace to the VDD pin and to the GND via should be kept as short as possible. Do not use vias between the decoupling capacitor and the VDD pin. In addition, a 10  $\mu$ F capacitor should be placed between VDD and VSS.

**Series Termination Resistor**: A series termination resistor is recommended if the distance between the outputs (SSCLK or REFCLK pins) and the load is over 1  $\frac{1}{2}$  inches. The nominal impedance of the SSCLK output is about 30  $\Omega$ . Use a 20  $\Omega$  resistor in series with the output to terminate a 50  $\Omega$  trace impedance and place a 20  $\Omega$  resistor as close to the SSCLK output as possible.

**Crystal and Crystal Load**: Only use a parallel resonant fundamental AT cut crystal. Do not use higher overtone crystals. To meet the crystal initial accuracy specification (in ppm) make sure that the external crystal load capacitor is matched to the crystal load specification. To determine the value of CL1 and CL2, use the following formula:

CL1 = CL2 = 2CL - (Cpin + Cp);

where CL is the load capacitance stated by the crystal manufacturer,

Cpin is the Si51214 pin capacitance (3 pF), and

Cp is the parasitic capacitance of the PCB traces.

**Example**: If a crystal with CL = 12 pF specification is used and Cp = 1 pF (parasitic PCB capacitance on PCB), 19 or 20 pF external capacitors from pins XIN (pin 2) and XOUT (Pin 3) to VSS are required. Users must verify Cp value.

#### Table 3.1. Crystal Specifications

| Equivalent Series Resistance (ESR) | Crystal Output Capacitance (CO) | Load Capacitance (CL) |

|------------------------------------|---------------------------------|-----------------------|

| <u>≤</u> 50 Ω                      | ≤ 3 pF                          | <u>≤</u> 13 pF        |

## 4. Electrical Specifications

#### Table 4.1. DC Electrical Specifications

$(V_{DD} = 1.8 \text{ V} \pm 5\%, \text{ C}_{L} = 10 \text{ pF}, \text{ T}_{A} = -40 \text{ to } 85 \text{ }^{\circ}\text{C})$

| Parameter                             | Symbol                            | Test Condition                                                                                                                          | Min                   | Тур  | Max                 | Unit |

|---------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|---------------------|------|

| Operating Voltage                     | V <sub>DD</sub>                   | V <sub>DD</sub> = 1.8 V ± 5%                                                                                                            | 1.71                  | 1.8  | 1.89                | V    |

| VDD Ramp Time                         | V <sub>DD_Ramp</sub>              | From 0 V to VDD <sub>min</sub>                                                                                                          | —                     | —    | 10                  | ms   |

| Output High Voltage                   | V <sub>OH</sub>                   | I <sub>OH</sub> = –4 mA                                                                                                                 | V <sub>DD</sub> – 0.5 | —    | _                   | V    |

| Output Low Voltage                    | V <sub>OL</sub>                   | I <sub>OL</sub> = 4 mA                                                                                                                  | _                     |      | 0.3                 | V    |

| Input High Voltage                    | V <sub>IH</sub>                   | CMOS Level                                                                                                                              | 0.7 V <sub>DD</sub>   | —    | _                   | V    |

| Input Low Voltage                     | V <sub>IL</sub>                   | CMOS Level                                                                                                                              | 0                     | _    | 0.3 V <sub>DD</sub> | V    |

| Operating Supply Current <sup>1</sup> | I <sub>DD</sub>                   | $F_{IN} = 12 \text{ MHz}, \text{ SSCLK1} = 12 \text{ MHz},$<br>$\text{SSCLK2} = 24 \text{ MHz}, C_L = 5 \text{ pF}, V_{DD}$<br>= 1.8  V | _                     | 5.5  | 9                   | mA   |

| Power Down Current                    | IDD <sub>PD</sub>                 |                                                                                                                                         | —                     | 0.5  | 0.65                | mA   |

| Nominal Output Impedance              | Z <sub>O</sub>                    |                                                                                                                                         | —                     | 30   | _                   | Ω    |

| Internal Pull-up/Pull-down Resistor   | R <sub>PUP</sub> /R <sub>PD</sub> | Pin 5                                                                                                                                   | _                     | 150k | _                   | Ω    |

| Input Pin Capacitance                 | C <sub>IN</sub>                   | Input pin capacitance                                                                                                                   | _                     | 3    | 5                   | pF   |

| Load Capacitance                      | CL                                | Clock outputs                                                                                                                           | _                     | _    | 10                  | pF   |

$1.\,I_{\text{DD}}$  depends on input and output frequency configurations.

#### Table 4.2. AC Electrical Specifications

(V<sub>DD</sub> = 1.8 V ±5%, C<sub>L</sub> = 10 pF, T<sub>A</sub> = -40 to 85 °C)

| Parameter                           | Symbol                         | Condition                         | Min | Тур | Max | Unit |

|-------------------------------------|--------------------------------|-----------------------------------|-----|-----|-----|------|

| Input Frequency Range               | F <sub>IN1</sub>               | Crystal input                     | 8   | _   | 48  | MHz  |

| Input Frequency Range               | F <sub>IN2</sub>               | Reference clock Input             | 3   | —   | 165 | MHz  |

| Output Frequency Range              | F <sub>OUT</sub>               | SSCLK1/2                          | 3   | —   | 133 | MHz  |

| Frequency Accuracy                  | F <sub>ACC</sub>               | Configuration dependent           | _   | 0   | _   | ppm  |

| Output Duty Cycle DC <sub>OUT</sub> |                                | Measured at V <sub>DDO</sub> /2   | 45  | 50  | 55  | %    |

|                                     |                                | F <sub>OUT</sub> ≤ 75 MHz         |     |     |     |      |

|                                     |                                | Measured at V <sub>DDO</sub> /2   | 40  | 50  | 60  | %    |

|                                     |                                | F <sub>OUT</sub> > 75 MHz         |     |     |     |      |

| Input Duty Cycle                    | DC <sub>IN</sub>               | CLKIN, CLKOUT through PLL         | 30  | 50  | 70  | %    |

| Output Rise/Fall Time               | t <sub>r</sub> /t <sub>f</sub> | C <sub>L</sub> = 10 pF, 20 to 80% | _   | 1   | 2   | ns   |

#### Si51214 Data Sheet • Electrical Specifications

| Parameter                                    | Symbol            | Condition                                                                                                    | Min | Тур | Max              | Unit   |

|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------------------|--------|

| Period Jitter                                | PJ <sub>1</sub>   | SSCLK1/2, at the same frequency                                                                              |     | 15  | 30               | ps rms |

|                                              | PJ <sub>2</sub>   | SSCLK1/2, at different output fre-<br>quencies <sup>1</sup>                                                  | _   | 35  | 105 <sup>2</sup> | ps rms |

| Cycle-to-Cycle Jitter                        | CCJ <sub>1</sub>  | SSCLK1/2, at the same frequency                                                                              | _   | 100 | 200              | ps     |

|                                              | CCJ <sub>2</sub>  | SSCLK1/2, at different output fre-<br>quencies <sup>1</sup>                                                  | _   | 150 | 305 <sup>2</sup> | ps     |

| Power-up Time                                | t <sub>PU</sub>   | Time from 0.9 V <sub>DD</sub> to valid frequencies at all clock outputs                                      |     | 1.2 | 5                | ms     |

| Output Enable Time                           | t <sub>OE</sub>   | Time from OE rising edge to ac-<br>tive at outputs SSCLK1/2 (asyn-<br>chronous), F <sub>OUT</sub> = 133 MHz  | _   | 15  | _                | ns     |

| Output Disable Time                          | t <sub>OD</sub>   | Time from OE falling edge to ac-<br>tive at outputs SSCLK1/2 (asyn-<br>chronous), F <sub>OUT</sub> = 133 MHz | _   | 15  | _                | ns     |

| Spread Spectrum Modulation Rate <sup>3</sup> | SS <sub>DEV</sub> |                                                                                                              | _   | 37  | —                | kHz    |

#### Note:

1. Example frequency configurations:

- 100 MHz, 75 MHz

- 100 MHz, 66 2/3 MHz

- 96 MHz, 133 1/3 MHz

- 2. Jitter performance depends on configuration and programming parameters.

- 3. The SS modulation rate is a fixed ratio of the reference frequency with values in the range of 30 kHz to 50 kHz based on the frequency plan.

#### Table 4.3. Absolute Maximum Conditions

| Parameter                               | Symbol             | Condition                   | Min   | Тур | Мах                  | Unit |

|-----------------------------------------|--------------------|-----------------------------|-------|-----|----------------------|------|

| Main Supply Voltage                     | V <sub>DD</sub>    |                             | -0.5  | _   | 2.4                  | V    |

| Input Voltage                           | V <sub>IN</sub>    | Relative to V <sub>SS</sub> | -0.5  | _   | V <sub>DD</sub> +0.5 | V    |

| Temperature, Storage                    | Τ <sub>S</sub>     | Non-functional              | -65   | _   | 150                  | °C   |

| Temperature, Operating Ambient          | T <sub>A</sub>     | Functional, I-temp          | -40   | _   | 85                   | °C   |

| ESD Protection (Human Body Mod-<br>el)  | ESD <sub>HBM</sub> | JEDEC (JESD 22-A114)        | -4000 | _   | 4000                 | V    |

| ESD Protection (Charge Device<br>Model) | ESD <sub>CDM</sub> | JEDEC (JESD 22-C101)        | -1500 | _   | 1500                 | V    |

| ESD Protection (Machine Model)          | ESD <sub>MM</sub>  | JEDEC (JESD 22-A115)        | -200  | _   | 200                  | V    |

Si51214 Data Sheet • Functional Description

## 5. Functional Description

#### 5.1 Input Frequency Range

The input frequency range is from 8.0 to 48.0 MHz for crystals and ceramic resonators. If an external clock is used, the input frequency range is from 3.0 to 165.0 MHz.

#### 5.2 Input Reference Power On Sequence

An external input clock should not be applied to XIN/CLKIN until VDD is stable. Wait until the voltage is approximately 90% of the final VDD value before enabling an external clock input. A crystal reference, on the other hand, can be applied anytime before or after VDD is stable.

#### 5.3 Output Frequency Range and Outputs

Up to two outputs can be programmed as SSCLK or REFCLK. SSCLK output can be synthesized to any value from 3 to 133 MHz with spread based on valid input frequency. The spread at the SSCLK pins can be enabled or disabled by the SSONb input control pin. If SSONb is used, when this pin is pulled high ( $V_{DD}$ ), the frequency at SSCLK pin is synthesized to the nominal value of the input frequency without spread. If low (GND), the frequency at SSCLK is synthesized to the nominal value of the input frequency with spread.

REFCLK is the buffered output of the oscillator and is the same frequency as the input frequency without spread. By using only low cost, fundamental mode crystals, the Si51214 can synthesize output frequency up to 133 MHz, eliminating the need for higher order crystals (Xtals) and crystal oscillators (XOs). This reduces the cost while improving the system clock accuracy, performance, and reliability.

#### 5.4 Programmable Spread Percent (%)

The spread percent (%) value is programmable to ±0.25%, ±0.5% or ±1% (center spread) for all SSCLK frequencies.

#### 5.5 SSONb or Frequency Select (FSEL)

The Si51214 pins 4 and 5 can be programmed as SSONb to enable or disable the programmed spread percent value. If SSONb is used, when this pin is pulled high ( $V_{DD}$ ),the frequency at SSCLK pin is synthesized to the nominal value of the input frequency without spread. If low (GND), the frequency at SSCLK is synthesized to the nominal value of the input frequency with spread. Pin 4 can also be programmed as frequency select (FSEL) function.

If FSEL function is used, the output pin can be programmed for different set of frequencies as selected by FSEL. SSCLK value can be any frequency from 3 to up to 133 MHz, but the spread % is the same percent value. REFCLK is the same frequency as the input reference clock. The set of frequencies in the table below are given as an example, using a 48 MHz crystal.

#### Table 5.1. Example Frequencies

| FSEL  | SSCLK1      |

|-------|-------------|

| Pin 4 | Pin 5       |

| 0     | 66 MHz, ±1% |

| 1     | 33 MHz, ±1% |

#### 5.6 Power Down (PD) or Output Enable (OE)

The Si51214 pin 5 can be programmed as PD input. Pin 4 and pin 5 can be programmed as OE input. PD turns off both PLL and output buffers whereas OE only disables the output buffers to Hi-Z. The OE function is asynchronous. Any requirement for synchronous operations (like glitchless output clock switching) needs to be handled externally.

Si51214 Data Sheet • Pin Description

## 6. Pin Description

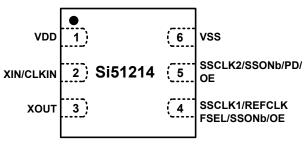

Figure 6.1. 6-Pin TDFN

#### Table 6.1. Si51214 6-Pin Descriptions

| Pin # | Name                        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDD                         | PWR  | 1.8 V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2     | XIN/CLKIN                   | I    | External crystal and clock input.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3     | XOUT                        | 0    | Crystal output. Leave this pin unconnected (floating) if an external clock input is used.                                                                                                                                                                                                                                                                                                                                               |

| 4     | SSCLK1/REFCLK/FSEL/SSONb/OE | I/O  | Programmable SSCLK1 or REFCLK output or MultiFunction con-<br>trol input. The frequency at this pin is synthesized by the inter-<br>nal PLL if programmed as SSCLK1 with or without spread. If<br>programmed as REFCLK, the output clock is a buffered output of<br>crystal or reference clock input. If programmed as a MultiFunction<br>control input, it can be OE, FSEL, and SSONb.                                                 |

| 5     | SSCLK2/OE/SSONb/PD          | I/O  | Programmable SSCLK2 output or MultiFunction control input. The frequency at this pin is synthesized by the internal PLL if programmed as SSCLK2 with or without spread. SSCLK2 output can also be programmed as a buffered output of crystal or reference clock input divided by N, $2 \le N \le 8$ . If programmed as a MultiFunction control input, it can be OE, PD, and SSONb. This pin cannot be programmed as FSEL control input. |

| 6     | VSS                         | GND  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

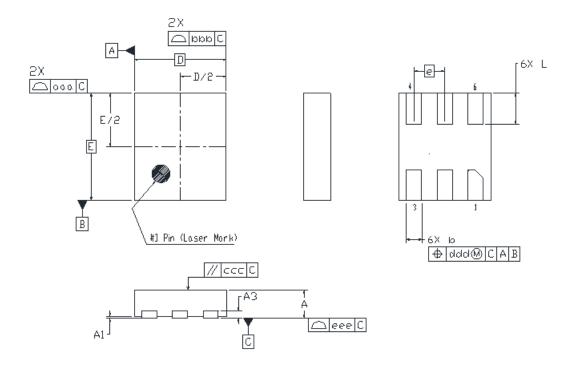

## 7. Package Outline

Figure 7.1. 6-pin TDFN

| Dimension | Min            | NOM      | Мах  |  |  |  |

|-----------|----------------|----------|------|--|--|--|

| A         | 0.70           | 0.75     | 0.80 |  |  |  |

| A1        | 0.00           | 0.02     | 0.05 |  |  |  |

| A3        |                | 0.20 REF |      |  |  |  |

| b         | 0.15           | 0.20     | 0.25 |  |  |  |

| D         | 1.20 BSC       |          |      |  |  |  |

| e         | 0.40 BSC       |          |      |  |  |  |

| E         | 1.40 BSC       |          |      |  |  |  |

| L         | 0.35 0.40 0.45 |          |      |  |  |  |

| ааа       | 0.05           |          |      |  |  |  |

| bbb       | 0.05           |          |      |  |  |  |

| CCC       | 0.10           |          |      |  |  |  |

| ddd       |                | 0.07     |      |  |  |  |

| eee       | 0.08           |          |      |  |  |  |

#### Si51214 Data Sheet • Package Outline

| Note:                                                                                                      |         |         |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|---------|---------|--|--|--|--|--|

| 1. All dimensions shown are in millimeters (mm) unless otherwise noted.                                    |         |         |  |  |  |  |  |

| 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.                                                      |         |         |  |  |  |  |  |

| 3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components. |         |         |  |  |  |  |  |

| M                                                                                                          | M-1994. | M-1994. |  |  |  |  |  |

Si51214 Data Sheet • PCB Land Pattern

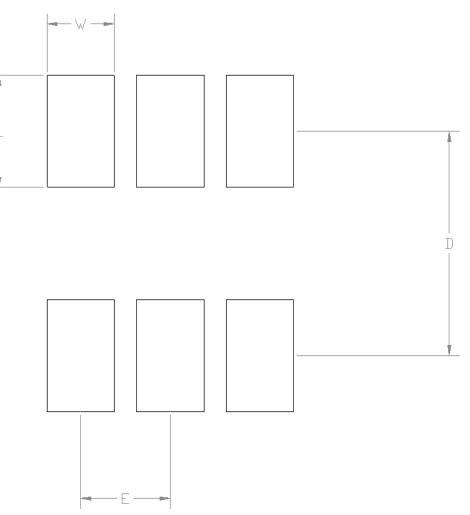

## 8. PCB Land Pattern

The figure below illustrates the PCB land pattern details for the device. The table below lists the values for the dimensions shown in the illustration.

| Dimension | mm   |

|-----------|------|

| D         | 1.00 |

| E         | 0.40 |

| L         | 0.5  |

| W         | 0.3  |

| Dimension                                                                                                                              | mm                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Note:                                                                                                                                  |                                                                            |

| General                                                                                                                                |                                                                            |

| 1. All dimensions shown are in millimeters (mm).                                                                                       |                                                                            |

| 2. This Land Pattern Design is based on the IPC-7351 guidelines                                                                        |                                                                            |

| <ol> <li>All dimensions shown are at Maximum Material Condition (MM<br/>allowance of 0.05 mm.</li> </ol>                               | C). Least Material Condition is calculated based on a fabrication          |

| Solder Mask Design                                                                                                                     |                                                                            |

| <ol> <li>All metal pads are to be non-solder mask defined (NSMD). Cle<br/>minimum, all the way around the pad.</li> </ol>              | arance between the solder mask and the metal pad is to be 60 $\mu\text{m}$ |

| Stencil Design                                                                                                                         |                                                                            |

| 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release |                                                                            |

| 2. The stencil thickness should be 0.125 mm (5 mils).                                                                                  |                                                                            |

| 3. The ratio of stencil aperture to land pad size should be 1:1 for                                                                    | all perimeter pads.                                                        |

| 4. A 2x1 array of 0.55 mm square openings on 0.90 mm pitch she                                                                         | ould be used for the center ground pad.                                    |

#### **Card Assembly**

1. A No-Clean, Type-3 solder paste is recommended.

2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 9. Revision History

#### 9.1 Revision 1.1

April 2, 2019

- Added VDD Ramp Time to Table 4.1 DC Electrical Specifications on page 6.

- Updated Ordering Guide for Product Revision B.

#### 9.2 Revision 1.0

April 20, 2016

- · Updated max clock input frequency to 165 MHz.

- Updated Operating Temperature to Industrial temperature, -40 °C to 85 °C.

- · Updated PD programmable active state.

- · Removed programmable output rise/fall time, SSEL.

- Updated Table 4.1 DC Electrical Specifications on page 6

- Updated Table 4.2 AC Electrical Specifications on page 6

- Updated pin descriptions in Pin Descriptions.

- · Updated customized part numbering nomenclature in Ordering Guide.

- Added land pattern drawing.

## SKYWORKS

## **ClockBuilder Pro**

Customize Skyworks clock generators, jitter attenuators and network synchronizers with a single tool. With CBPro you can control evaluation boards, access documentation, request a custom part number, export for in-system programming and more!

www.skyworksinc.com/CBPro

C

Portfolio www.skyworksinc.com/ia/timing

www.skyworksinc.com/CBPro

Quality www.skyworksinc.com/quality

Support & Resources www.skyworksinc.com/support

## Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5<sup>®</sup>, SkyOne<sup>®</sup>, SkyBlue<sup>™</sup>, Skyworks Green<sup>™</sup>, Clockbuilder<sup>®</sup>, DSPLL<sup>®</sup>, ISOmodem<sup>®</sup>, ProSLIC<sup>®</sup>, and SiPHY<sup>®</sup> are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.