# 4-PLL ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER ATTENUATOR

#### **Features**

- Highly-integrated, 4 PLL clock multiplier/jitter attenuator

- Four independent DSPLLs support any-frequency synthesis and jitter attenuation

- 8 inputs/8 outputs

- Each DSPLL can generate any frequency from 2 kHz to 808 MHz from a 2 kHz to 710 MHz input

- Ultra-low jitter clock outputs: 350 fs rms (12 kHz–20 MHz) and 410 fs rms (50 kHz–80 MHz) typical

- Meets ITU-T G.8251 and Telcordia GR-253-CORE OC-192 jitter specifications

- Supports all ITU G.709 and any custom FEC ratios (239/237, 255/238, 255/237, 255/236, 253/226)

- Integrated loop filter with programmable bandwidth

- Simultaneous free-run and synchronous operation

- Automatic/manual hitless input clock switching

- Selectable output clock signal format (LVPECL, LVDS, CML, CMOS)

- LOL and interrupt alarm outputs

- I<sup>2</sup>C programmable

- Single 1.8 V ±5% or 2.5 V ±10% operation with high PSRR on-chip voltage regulator

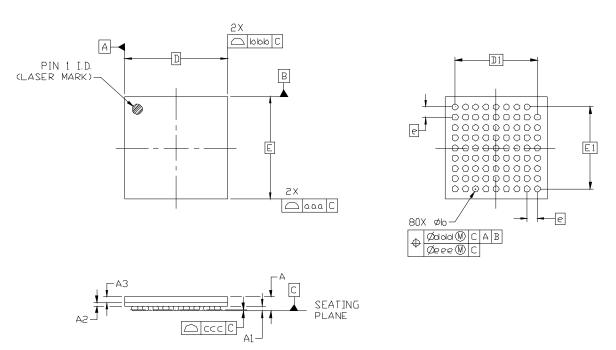

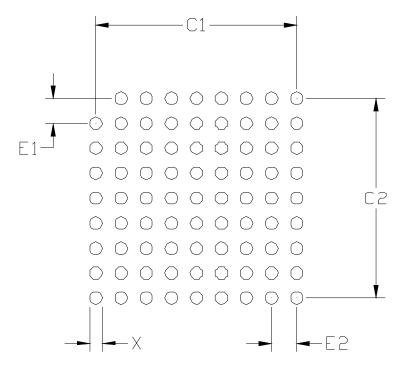

- 10x10 mm PBGA

## Applications

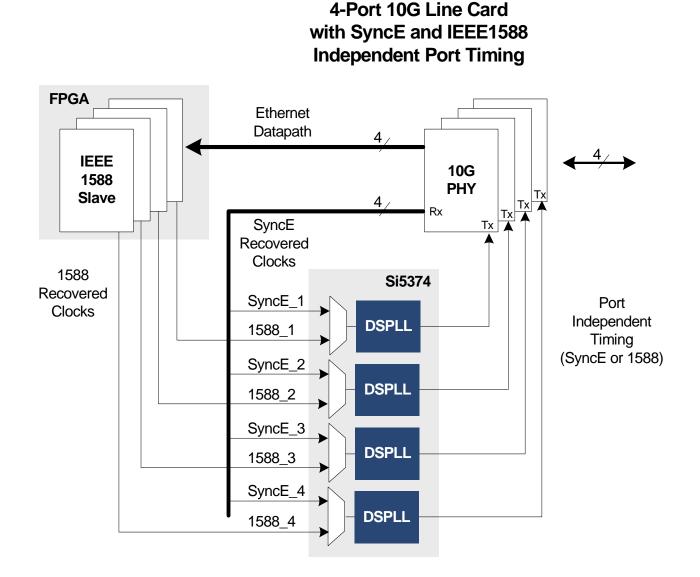

- High-density, any-port, any-protocol, any-frequency line cards

- ITU-T G.709 OTN custom FEC

- 10/40/100G

- OC-48/192, STM-16/64

- 1/2/4/8/10G Fibre Channel

- GbE/10 GbE Synchronous Ethernet

- Carrier Ethernet, multi-service switches and routers

- MSPP, ROADM, P-OTS, muxponders

#### Description

The Si5374 is a highly-integrated, 4-PLL, jitter-attenuating precision clock multiplier for applications requiring sub-1 ps jitter performance. Each of the DSPLL® clock multiplier engines accepts two input clocks ranging from 2 kHz to 710 MHz and generates two independent synchronous output clocks ranging from 2 kHz to 808 MHz. The device provides virtually any frequency translation combination across this operating range. For asynchronous, free-running clock generation applications, the Si5374's reference oscillator can be used as a clock source for any of the four DSPLLs. The Si5374 input clock frequency and clock multiplication ratio are programmable through an I<sup>2</sup>C interface. The Si5374 is based on Skyworks Solutions' third-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly-integrated PLL solution that eliminates the need for external VCXO and loop filter components. Each DSPLL loop bandwidth is digitally-programmable, providing itter performance optimization at the application level. The device operates from a single 1.8 or 2.5 V supply with on-chip voltage regulators with excellent PSRR. The Si5374 is ideal for providing clock multiplication and jitter attenuation in high-port-count optical line cards requiring independent timing domains.

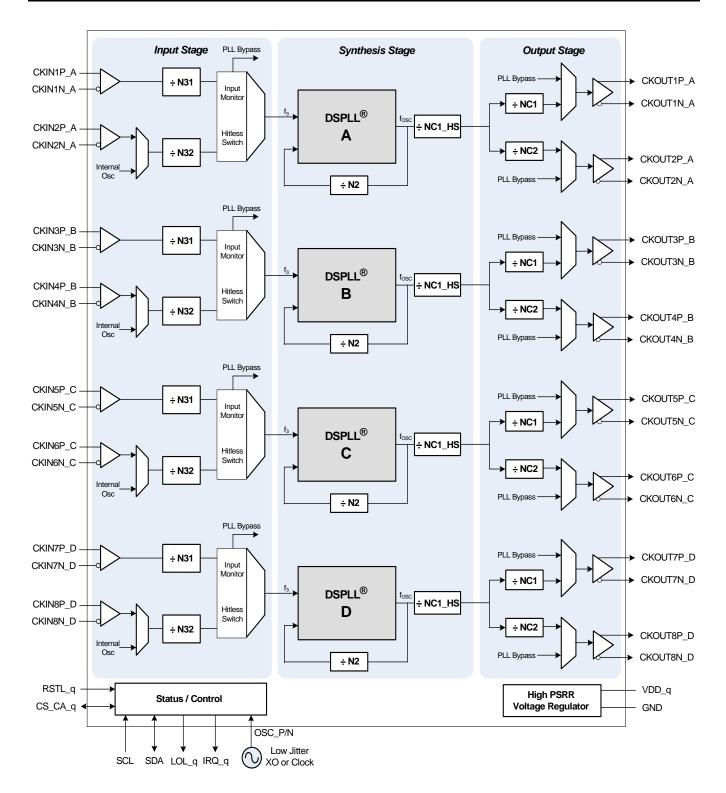

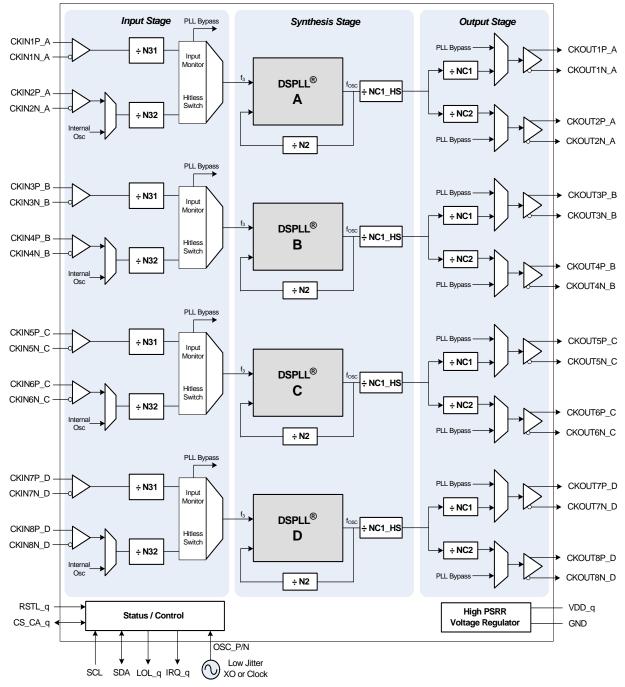

# **Functional Block Diagram**

2 Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 1.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • March 14, 2022

# TABLE OF CONTENTS

# Section

# Page

| 1. Electrical Specifications                      |

|---------------------------------------------------|

| 5. Si5374 Application Examples and Suggestions    |

| 5.1. Schematic and PCB Layout                     |

| 5.2. Thermal Considerations                       |

| 5.3. SCL Leakage                                  |

| 5.4. RSTL_x Pins                                  |

| 5.5. Reference Oscillator Selection               |

| 5.6. Alarms                                       |

| 5.7. OSC_P and OSC_N Connection                   |

| 6. Register Map                                   |

| 7. Register Descriptions                          |

| 7.1. ICAL                                         |

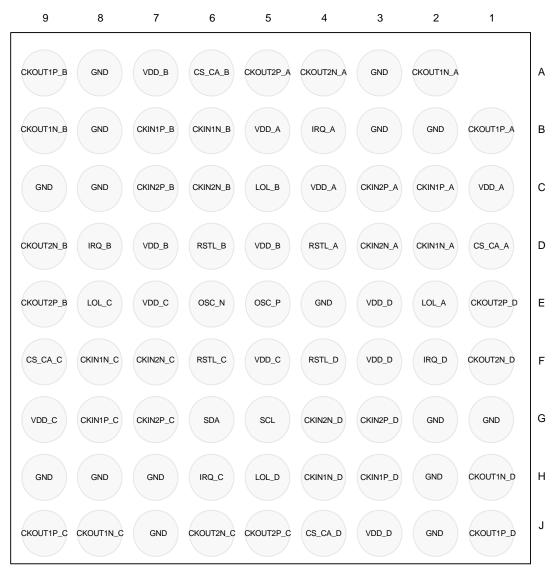

| 8. Pin Descriptions: Si5374                       |

| 9. Ordering Guide                                 |

| 10. Package Outline                               |

| 11. Recommended PCB Layout                        |

| 12. Top Markings                                  |

| 12.1. Si5374 Top Marking (PBGA, Lead-Free)66      |

| 12.2. Top Marking Explanation (PBGA, Lead-Free)   |

| 12.3. Si5374 Top Marking (PBGA, Lead-Finish)      |

| 12.4. Top Marking Explanation (PBGA, Lead-Finish) |

| Document Change List                              |

| Contact Information                               |

# **1. Electrical Specifications**

#### **Table 1. Recommended Operating Conditions**

| Parameter                                                                                                                                                                                                                            | Symbol          | Test Condition | Min  | Тур | Max  | Unit |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------|-----|------|------|--|

| Ambient Temperature                                                                                                                                                                                                                  | T <sub>A</sub>  |                | -40  | 25  | 85   | °C   |  |

| Supply Voltage during                                                                                                                                                                                                                | V <sub>DD</sub> | 2.5 V Nominal  | 2.25 | 2.5 | 2.75 | V    |  |

| Normal Operation                                                                                                                                                                                                                     |                 | 1.8 V Nominal  | 1.71 | 1.8 | 1.89 | V    |  |

| Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.<br>Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated. |                 |                |      |     |      |      |  |

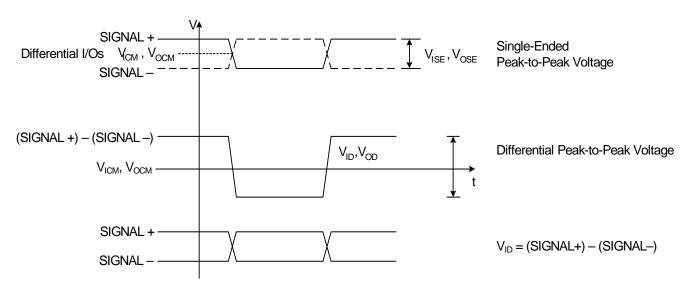

#### **Figure 1. Differential Voltage Characteristics**

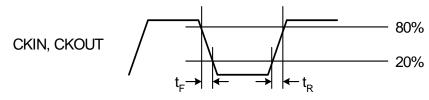

Figure 2. Rise/Fall Time Characteristics

4

#### **Table 2. DC Characteristics**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                   | Symbol             | Test Condition                                        | Min                       | Тур  | Max                   | Unit            |

|-------------------------------------------------------------|--------------------|-------------------------------------------------------|---------------------------|------|-----------------------|-----------------|

| Supply Current <sup>1</sup>                                 | I <sub>DD</sub>    | LVPECL Format<br>622.08 MHz Out<br>All CKOUTs Enabled | —                         | 1000 | 1100                  | mA              |

|                                                             |                    | LVPECL Format<br>622.08 MHz Out<br>4 CKOUTs Enabled   | —                         | 870  | 970                   | mA              |

|                                                             |                    | CMOS Format<br>19.44 MHz Out<br>All CKOUTs Enabled    | —                         | 820  | 940                   | mA              |

|                                                             |                    | CMOS Format<br>19.44 MHz Out<br>4 CKOUTs Enabled      | —                         | 780  | 880                   | mA              |

|                                                             |                    | Disable Mode                                          | —                         | 660  | —                     | mA              |

| CKINn Input Pins <sup>2</sup>                               |                    |                                                       |                           |      |                       |                 |

| Input Common Mode<br>Voltage (Input Thresh-<br>old Voltage) | V <sub>ICM</sub>   | 1.8 V ± 5%                                            | 0.9                       | _    | 1.4                   | V               |

|                                                             |                    | 2.5 V ± 10%                                           | 1                         | _    | 1.7                   | V               |

| Input Resistance                                            | CKN <sub>RIN</sub> | Single-ended                                          | 20                        | 40   | 60                    | kΩ              |

| Single-Ended Input<br>Voltage Swing                         | V <sub>ISE</sub>   | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2                       | —    | —                     | V <sub>PP</sub> |

| (See Absolute Specs)                                        |                    | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 1.        | 0.25                      | —    | —                     | V <sub>PP</sub> |

| Differential Input<br>Voltage Swing                         | V <sub>ID</sub>    | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2                       | _    | —                     | V <sub>PP</sub> |

| (See Absolute Specs)                                        |                    | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 1.        | 0.25                      | —    | —                     | V <sub>PP</sub> |

| Output Clocks (CKOU                                         | Tn) <sup>3,4</sup> |                                                       |                           |      |                       |                 |

| Common Mode                                                 | CKO <sub>VCM</sub> | LVPECL 100 $\Omega$ load line-to-line                 | V <sub>DD</sub> –<br>1.42 | _    | V <sub>DD</sub> –1.25 | V               |

| Differential Output                                         | CKO <sub>VD</sub>  | LVPECL 100 Ω load<br>line-to-line                     | 1.1                       | _    | 1.9                   | $V_{PP}$        |

5

## Table 2. DC Characteristics (Continued)

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                   | Symbol               | Test Condition                                | Min                      | Тур                   | Max   | Unit             |

|-----------------------------------------------------------------------------|----------------------|-----------------------------------------------|--------------------------|-----------------------|-------|------------------|

| Single Ended Output<br>Swing                                                | CKO <sub>VSE</sub>   | LVPECL 100 Ω load<br>line-to-line             | 0.5                      | —                     | 0.93  | V <sub>PP</sub>  |

| Differential Output<br>Voltage                                              | CKO <sub>VD</sub>    | CML 100 Ω load<br>line-to-line                | 350                      | 425                   | 500   | mV <sub>PP</sub> |

| Common Mode Output<br>Voltage                                               | CKO <sub>VCM</sub>   | CML 100 Ω load<br>line-to-line                | —                        | V <sub>DD</sub> -0.36 |       | V                |

| Differential Output<br>Voltage                                              | CKO <sub>VD</sub>    | LVDS 100 $\Omega$ load line-to-line           | 500                      | 700                   | 900   | mV <sub>PP</sub> |

|                                                                             |                      | Low Swing LVDS 100 $\Omega$ load line-to-line | 350                      | 425                   | 500   | mV <sub>PP</sub> |

| Common Mode Output<br>Voltage                                               | CKO <sub>VCM</sub>   | LVDS 100 Ω load<br>line-to-line               | 1.125                    | 1.2                   | 1.275 | V                |

| Differential Output<br>Resistance                                           | CKO <sub>RD</sub>    | CML, LVPECL, LVDS                             | —                        | 200                   | _     | Ω                |

| Output Voltage Low                                                          | CKO <sub>VOLLH</sub> | CMOS                                          | —                        | —                     | 0.4   | V                |

| Output Voltage High                                                         | CKO <sub>VOHLH</sub> | V <sub>DD</sub> = 1.71 V<br>CMOS              | 0.8 x<br>V <sub>DD</sub> | —                     | _     | V                |

| Output Drive Current<br>(CMOS driving into                                  | СКО <sub>Ю</sub>     | ICMOS[1:0] = 11<br>V <sub>DD</sub> = 1.8 V    | —                        | 7.5                   | —     | mA               |

| $CKO_{VOL}$ for output low<br>or $CKO_{VOH}$ for output<br>high. CKOUT+ and |                      | ICMOS[1:0] = 10<br>V <sub>DD</sub> = 1.8 V    | _                        | 5.5                   |       | mA               |

| CKOUT– shorted<br>externally)                                               |                      | ICMOS[1:0] = 01<br>V <sub>DD</sub> = 1.8 V    | _                        | 3.5                   |       | mA               |

|                                                                             |                      | ICMOS[1:0] = 00<br>V <sub>DD</sub> = 1.8 V    | _                        | 1.75                  | _     | mA               |

|                                                                             |                      | ICMOS[1:0] = 11<br>V <sub>DD</sub> = 2.5 V    | _                        | 20                    | _     | mA               |

|                                                                             |                      | ICMOS[1:0] = 10<br>V <sub>DD</sub> = 2.5 V    | _                        | 15                    | _     | mA               |

|                                                                             |                      | ICMOS[1:0] = 01<br>V <sub>DD</sub> = 2.5 V    | _                        | 10                    | _     | mA               |

|                                                                             |                      | ICMOS[1:0] = 00<br>V <sub>DD</sub> = 2.5 V    | _                        | 5                     | —     | mA               |

1. Current draw is independent of supply voltage.

2. No under- or overshoot is allowed.

**3.** LVPECL outputs require nominal V<sub>DD</sub> = 2.5 V. **4.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

6

## Table 2. DC Characteristics (Continued)

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40$  to 85 °C)

| Parameter                                                                                             | Symbol                                             | Test Condition                         | Min                      | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|--------------------------|-----|-----|------|

| 2-Level LVCMOS Inpu                                                                                   | It Pins                                            |                                        |                          |     |     |      |

| Input Voltage Low                                                                                     | V <sub>IL</sub>                                    | V <sub>DD</sub> = 1.71 V               |                          | _   | 0.5 | V    |

|                                                                                                       |                                                    | V <sub>DD</sub> = 2.25 V               | —                        | —   | 0.7 | V    |

| Input Voltage High                                                                                    | V <sub>IH</sub>                                    | V <sub>DD</sub> = 1.89 V               | 1.4                      | —   |     | V    |

|                                                                                                       |                                                    | V <sub>DD</sub> = 2.25 V               | 1.8                      | —   |     | V    |

| LVCMOS Output Pins                                                                                    | 1 1                                                |                                        |                          |     | L   |      |

| Output Voltage Low                                                                                    | V <sub>OL</sub>                                    | IO = 2 mA<br>V <sub>DD</sub> = 1.71 V  | —                        | _   | 0.4 | V    |

| Output Voltage Low                                                                                    |                                                    | IO = 2 mA<br>V <sub>DD</sub> = 2.25 V  | —                        | _   | 0.4 | V    |

| Output Voltage High                                                                                   | V <sub>OH</sub>                                    | IO = -2 mA<br>V <sub>DD</sub> = 1.71 V | V <sub>DD</sub> -<br>0.4 | _   | _   | V    |

| Output Voltage High                                                                                   |                                                    | IO = -2 mA<br>V <sub>DD</sub> = 2.25 V | V <sub>DD</sub> –<br>0.4 | _   | _   | V    |

| Notes:<br>1. Current draw is ind<br>2. No under- or overs<br>3. LVPECL outputs re<br>4. LVPECL CML LV | shoot is allowed.<br>equire nominal V <sub>D</sub> |                                        | 622 08 MH7               |     |     |      |

4. LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

#### Table 3. AC Characteristics

(V<sub>DD</sub> = 1.8 ± 5%, 2.5 ±10%, T<sub>A</sub> = –40 to 85 °C)

| Parameter                                                                | Symbol             | Test Condition                                                                                          | Min        | Тур             | Max   | Unit            |

|--------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|------------|-----------------|-------|-----------------|

| Single-Ended Referer                                                     | nce Clock Inp      | ut Pin OSC_P (OSC_N with                                                                                | cap to GND | )) <sup>1</sup> |       |                 |

| OSC_P to OSC_N<br>Resistance                                             | OSC <sub>RIN</sub> | RATE_REG = 0101 or<br>0110, ac coupled                                                                  | _          | 100             | _     | Ω               |

| Input Voltage Swing                                                      | OSC <sub>VPP</sub> | RATE_REG = 0101 or<br>0110, ac coupled                                                                  | 0.5        | —               | 1.2   | V <sub>PP</sub> |

| Differential Reference                                                   | Clock Input        | Pins (OSC_P/OSC_N) <sup>1</sup>                                                                         |            |                 |       |                 |

| Input Voltage Swing                                                      | OSC <sub>VPP</sub> | RATE_REG = 0101 or<br>0110, ac coupled                                                                  | 0.5        | —               | 2.4   | V <sub>PP</sub> |

| CKINn Input Pins                                                         |                    |                                                                                                         |            |                 |       |                 |

| Input Frequency                                                          | CKN <sub>F</sub>   |                                                                                                         | 0.002      | —               | 710   | MHz             |

| Input Duty Cycle<br>(Minimum Pulse<br>Width)                             | CKN <sub>DC</sub>  | Whichever is smaller<br>(i.e., the 40% / 60%<br>limitation applies only<br>to high-frequency<br>clocks) | 40         |                 | 60    | %               |

|                                                                          |                    |                                                                                                         | 2          | —               | —     | ns              |

| Input Rise/Fall Time                                                     | CKN <sub>TRF</sub> | 20–80%<br>See Figure 2                                                                                  | —          | —               | 11    | ns              |

| CKOUTn Output Pins                                                       |                    |                                                                                                         |            |                 |       |                 |

| Output Frequency<br>(Output not config-<br>ured for CMOS or<br>Disabled) | СКО <sub>F</sub>   |                                                                                                         | 0.002      | _               | 808   | MHz             |

| Maximum Output<br>Frequency in CMOS<br>Format                            | СКО <sub>F</sub>   |                                                                                                         | _          | _               | 212.5 | MHz             |

| Output Rise/Fall<br>(20–80 %) @<br>622.08 MHz output                     | CKO <sub>TRF</sub> | Output not configured for<br>CMOS or Disabled<br>See Figure 2                                           | _          | 230             | 350   | ps              |

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output                       | CKO <sub>TRF</sub> | $CMOS Output$ $V_{DD} = 1.71$ $C_{LOAD} = 5 \text{ pF}$                                                 | _          | _               | 8     | ns              |

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output                       | CKO <sub>TRF</sub> | CMOS Output<br>$V_{DD} = 2.25$<br>$C_{LOAD} = 5 pF$                                                     | _          | _               | 2     | ns              |

2. Input to output skew after an ICAL is not controlled and can be any value.

8

## Table 3. AC Characteristics (Continued)

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40$  to 85 °C)

| Symbol              | Test Condition                                                                                          | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Тур                                                                                                                                                                                                                                            | Max                                                                                                                                                                                                                                                                                                                | Unit                                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKO <sub>DC</sub>   | 100 Ω Load<br>Line-to-Line<br>Measured at 50% Point<br>(differential)                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                              | ±40                                                                                                                                                                                                                                                                                                                | ps                                                                                                                                                                                                                                             |

|                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                |

| t <sub>RSTMN</sub>  |                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                  | μs                                                                                                                                                                                                                                             |

| t <sub>READY</sub>  |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                              | 10                                                                                                                                                                                                                                                                                                                 | ms                                                                                                                                                                                                                                             |

|                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ·                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                |

| t <sub>RF</sub>     | C <sub>LOAD</sub> = 20pf<br>See Figure 2                                                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                             |

| LOS <sub>TRIG</sub> | From last CKINn ↑ to ↓<br>Internal detection of LOSn<br>N3 ≠ 1                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                              | 4.5 x N3                                                                                                                                                                                                                                                                                                           | T <sub>CKIN</sub>                                                                                                                                                                                                                              |

| <sup>t</sup> CLRLOL | ↓LOS to ↓LOL<br>Fold = Fnew<br>Stable OSC_P, OSC_N<br>reference                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                  | ms                                                                                                                                                                                                                                             |

|                     | CKO <sub>DC</sub><br>t <sub>RSTMN</sub><br>t <sub>READY</sub><br>t <sub>RF</sub><br>LOS <sub>TRIG</sub> | CKO <sub>DC</sub> 100 Ω Load<br>Line-to-Line<br>Measured at 50% Point<br>(differential)         t <sub>RSTMN</sub> Image: Close transmission of the second seco | $\begin{array}{c c c c c c c c } \hline CKO_{DC} & 100 \ \Omega \ Load \\ Line-to-Line \\ Measured at 50\% \ Point \\ (differential) \end{array} & \\ \hline $ | CKO <sub>DC</sub> 100 Ω Load<br>Line-to-Line<br>Measured at 50% Point<br>(differential) $t_{RSTMN}$ 1 $t_{READY}$ $t_{RF}$ $C_{LOAD} = 20pf$<br>See Figure 225LOS <sub>TRIG</sub> From last CKINn ↑ to ↓<br>Internal detection of LOSn<br>N3 ≠ 1 $t_{CLRLOL}$ ↓LOS to ↓LOL<br>Fold = Fnew<br>Stable OSC_P, OSC_N10 | $\begin{array}{c c c c c c c c } \hline CKO_{DC} & 100 \ \Omega \ Load \\ Line-to-Line \\ Measured at 50\% \ Point \\ (differential) \end{array} & \hline & - & - & \pm 40 \end{array}$ $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

#### Table 3. AC Characteristics (Continued)

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                    | Symbol            | Test Condition                                                                                                                                           | Min | Тур | Max | Unit |

|----------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Device Skew <sup>2</sup>                     |                   |                                                                                                                                                          |     |     |     |      |

| Output Clock Skew                            | t <sub>SKEW</sub> | ↑ of CKOUTn to ↑ of<br>CKOUT_m, CKOUTn<br>and CKOUT_m at same<br>frequency and signal<br>format<br>PHASEOFFSET = 0<br>CKOUT_ALWAYS_ON = 1<br>SQ_ICAL = 1 | _   | _   | 100 | ps   |

| Phase Change due to<br>Temperature Variation | t <sub>TEMP</sub> | Max phase changes from<br>-40 to +85 °C                                                                                                                  |     | 300 | 500 | ps   |

| Notes:                                       |                   |                                                                                                                                                          |     |     |     |      |

**1.** A crystal may not be used in place of an oscillator. 2. Input to output skew after an ICAL is not controlled and can be any value.

#### **Table 4. Microprocessor Control**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                               | Symbol              | Test Condition                       | Min                   | Тур | Max                    | Unit |

|-----------------------------------------|---------------------|--------------------------------------|-----------------------|-----|------------------------|------|

| I <sup>2</sup> C Bus Lines (SDA, S      | CL)                 |                                      |                       |     |                        |      |

| Input Voltage Low                       | VIL <sub>I2C</sub>  |                                      | —                     | _   | 0.25 x V <sub>DD</sub> | V    |

| Input Voltage High                      | VIH <sub>I2C</sub>  |                                      | 0.7 x V <sub>DD</sub> | —   | V <sub>DD</sub>        | V    |

| Hysteresis of Schmitt<br>Trigger Inputs | VHYS <sub>I2C</sub> | V <sub>DD</sub> = 1.8 V              | 0.1 x V <sub>DD</sub> | —   | —                      | V    |

| ingger inputs                           |                     | V <sub>DD</sub> = 2.5                | $0.05 \times V_{DD}$  | _   | —                      | V    |

| Output Voltage Low                      | VOL <sub>I2C</sub>  | V <sub>DD</sub> = 1.8 V<br>IO = 3 mA | _                     | —   | 0.2 x V <sub>DD</sub>  | V    |

|                                         |                     | V <sub>DD</sub> = 2.5<br>IO = 3 mA   | —                     | —   | 0.4                    | V    |

10

#### Table 5. Performance Specifications

$V_{DD} = 1.8 \text{ V} \pm 5\% \text{ or } 2.5 \text{ V} \pm 10\%, \text{ T}_{A} = -40 \text{ to } 85 \text{ }^{\circ}\text{C}$

| Parameter                                        | Symbol              | Test Condition                                                                                    | Min     | Тур  | Max | Unit        |

|--------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------|---------|------|-----|-------------|

| PLL Performance <sup>1</sup>                     |                     |                                                                                                   |         |      |     |             |

| Lock Time <sup>2</sup> Si5374B-A-xL <sup>3</sup> | t <sub>LOCKMP</sub> | Start of ICAL to $\downarrow$ of LOL,                                                             | —       | 1    | 1.5 | S           |

| Si5374C-A-xL                                     |                     | FASTLOCK enabled                                                                                  | —       | 0.8  | 1.0 |             |

| Settle Time <sup>2</sup> Si5374B-A-xL            | t <sub>SETTLE</sub> | Start of ICAL to F <sub>OUT</sub> within<br>5 ppm of final value                                  | _       | 1.2  | 1.5 | S           |

| Si5374C-A-xL                                     |                     |                                                                                                   | _       | 4.2  | 5.0 |             |

| Output Clock Phase Change                        | t <sub>P_STEP</sub> | After clock switch $f3 \ge 128 \text{ kHz}$                                                       | —       | 200  | _   | ps          |

| Closed Loop Jitter Peaking                       | J <sub>PK</sub>     |                                                                                                   | —       | 0.05 | 0.1 | dB          |

| Jitter Tolerance                                 | J <sub>TOL</sub>    | Jitter Frequency ≥ Loop<br>Bandwidth                                                              | 5000/BW |      | _   | ns<br>pk-pk |

| Phase Noise                                      | CKO <sub>PN</sub>   | 1 kHz Offset                                                                                      | —       | -106 |     | dBc/Hz      |

| fout = 622.08 MHz                                |                     | 10 kHz Offset                                                                                     | —       | -114 |     | dBc/Hz      |

|                                                  |                     | 100 kHz Offset                                                                                    | —       | -116 |     | dBc/Hz      |

|                                                  |                     | 1 MHz Offset                                                                                      | —       | -132 |     | dBc/Hz      |

| Spurious Noise                                   | SP <sub>SPUR</sub>  | Max spur @ n x F3<br>(n ≥ 1, n x F3 < 100 MHz)                                                    | —       | -70  | _   | dBc         |

| Jitter Generation                                | J <sub>GEN</sub>    | f <sub>IN</sub> = f <sub>OUT</sub> = 622.08 MHz,<br>BW = 120 Hz<br>LVPECL output<br>12 kHz–20 MHz | _       | 350  | 410 | fs rms      |

|                                                  |                     | 50 kHz–80 MHz                                                                                     | _       | 410  |     | fs rms      |

#### Notes:

**1.** fin = fout = 622.08 MHz; BW = 7 Hz; LVDS, OSC = .121.109 MHz.

2. Lock and settle time performance is dependent on the frequency plan and the OSC\_P/OSC\_N reference frequency and LOCKT setting (see application note, "AN803: Lock and Settling Time Considerations for the Si5324/27/69/74 Any-Frequency Jitter Attenuating Clock ICs". Visit the Skyworks Solutions Technical Support web page at: https://www.skyworksinc.com/en/Support to submit a technical support request regarding the lock time of your frequency plan.

**3.** LOCKT = 3.3 ms.

## Table 6. Thermal Characteristics<sup>1,2</sup>

| Parameter                                 | Symbol | Test Condition                                                  | Min  | Тур                  | Max | Unit |

|-------------------------------------------|--------|-----------------------------------------------------------------|------|----------------------|-----|------|

| Maximum Junction<br>Temperature           |        |                                                                 | _    | 125                  |     | °C   |

| Thermal Resistance<br>Junction to Ambient | ΑLΦ    | Still Air<br>Air Flow 1 m/s<br>Air Flow 2 m/s<br>Air Flow 3 m/s | <br> | 16<br>14<br>13<br>12 |     | °C/W |

| Thermal Resistance<br>Junction to Case    | φJC    | Still Air                                                       | —    | 3.4                  |     | °C/W |

Notes:

1. In most circumstances the Si5374 does not require special thermal management. A system level thermal analysis is strongly recommend. Contact Skyworks Solutions applications for further details if required.

2. Thermal characteristic for the 80-pin Si5374 on an 8-layer PCB.

#### **Table 7. Absolute Maximum Ratings**

| Parameter                                                        | Symbol             | Value                           | Unit |

|------------------------------------------------------------------|--------------------|---------------------------------|------|

| DC Supply Voltage                                                | V <sub>DD</sub>    | -0.5 to 2.8                     | V    |

| LVCMOS Input Voltage                                             | V <sub>DIG</sub>   | –0.3 to (V <sub>DD</sub> + 0.3) | V    |

| CLKINnP/N_q                                                      | CKN <sub>VIN</sub> | 0 to V <sub>DD</sub>            | V    |

| OSC_P, OSC_N Voltage Limits                                      | OSC <sub>VIN</sub> | 0 to 1.2                        | V    |

| Operating Junction Temperature                                   | T <sub>JCT</sub>   | -55 to 150                      | °C   |

| Storage Temperature Range                                        | T <sub>STG</sub>   | -55 to 150                      | °C   |

| ESD HBM Tolerance (100 pF, 1.5 k); All pins<br>except CKINnP/N-q |                    | 2                               | kV   |

| ESD MM Tolerance; All pins except<br>CKINnP/N_q                  |                    | 200                             | V    |

| ESD HBM Tolerance (100 pF, 1.5 k);<br>CKINnP/N_q                 |                    | 700                             | V    |

| ESD MM Tolerance; CKINnP/N_q                                     |                    | 125                             | V    |

| Latch-Up Tolerance                                               |                    | JESD78 Compliant                |      |

**Note:** Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

<sup>12</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 1.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • March 14, 2022

# 2. Typical Application Schematic

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com 13 Rev. 1.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • March 14, 2022

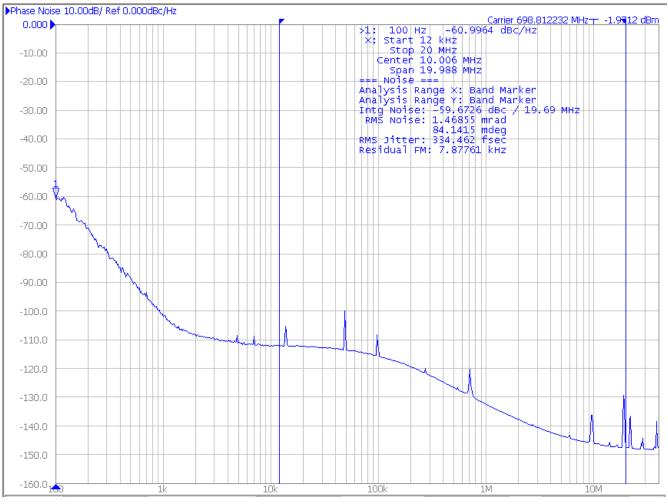

# 3. Typical Phase Noise Plot

- 19.44 MHz input

- 698.8123 MHz OTU4 output

- 334 fs RMS jitter (12 kHz to 20 MHz)

Figure 3. Typical Phase Noise Plot

# 4. Functional Description

Figure 4. Functional Block Diagram

The Si5374 is a highly integrated jitter-attenuating clock multiplier that integrates four fully independent DSPLLs and provides ultra-low jitter generation with less than 410 fs RMS. Configuration and control of the Si5374 is mainly handled through the  $I^2C$  interface. The device accepts clock inputs ranging from 2 kHz to 710 MHz and generates independent, synchronous clock outputs ranging from 2 kHz to 808 MHz for each DSPLL. Virtually any frequency translation (M/N) combination across its operating range is supported. The Si5374 supports a digitally programmable loop bandwidth that can range from 4 to 525 Hz requiring no external loop filter components. An external single-ended or differential reference clock or XO is required for the device to enable ultra-low jitter generation and jitter attenuation.

The device monitors each input clock for loss-of-signal (LOS) and provides a LOS alarm when missing pulses on any of the input clocks are detected. The device monitors the lock status of each DSPLL and provides a Loss-of-Lock (LOL) alarm when the DSPLL is unlocked. The lock detect algorithm continuously monitors the phase of the selected input clock in relation to the phase of the feedback clock. See application note, "AN803: Lock and Settling Time Considerations for the Si5324/27/69/74 Any-Frequency Jitter Attenuating Clock ICS."

The Si5374 provides a holdover capability that allows the device to continue generation of a stable output clock when the input reference is lost. The reference oscillator can be internally routed into CKIN2\_q, so freerunning clock generation is supported for each DSPLL offering simultaneous synchronous and asynchronous operation.

The output drivers are configurable to support common signal formats, such as LVPECL, LVDS, CML, and CMOS loads. If the CMOS signal format is selected, each differential output buffer generates two in-phase CMOS clocks at the same frequency. For system-level debugging, a DSPLL bypass mode drives the clock output directly from the selected input clock, bypassing the internal DSPLL.

Skyworks Solutions offers a PC-based software utility, Si537xDSPLL*sim* that can be used to determine valid frequency plans and loop bandwidth settings to simplify device setup. Si537xDSPLL*sim* provides the optimum input, output, and feedback divider values for a given input frequency and clock multiplication ratio that minimizes phase noise. This utility can be downloaded from https://www.skyworksinc.com/en/Application-Pages/DSPLL. For further assistance, refer to the Si53xx Any-Frequency Precision Clocks Family Reference Manual.

# 5. Si5374 Application Examples and Suggestions

## 5.1. Schematic and PCB Layout

For a typical application schematic and PCB layout, see the Si537x-EVB Evaluation Board User's Guide, which can be downloaded from https://www.skyworksinc.com/technical%20documents.

In order to preserve the ultra low jitter of the Si5374 in applications where the four different DSPLL's are each operating at different frequency, special care and attention must be paid to the PCB layout. The following is a list of rules that should be observed:

- The four Vdd supplies should be isolated from one another with four ferrite beads. They should be separately bypassed with capacitors that are located very close to the Si5374 device.

- 2. Use a solid and undisturbed ground plane for the Si5374 and all of the clock input and output return paths.

- 3. For applications that wish to logically connect the four RESET signals, do not tie them together underneath the BGA package. Instead connect them outside of the BGA footprint.

- 4. As much as is possible, do not route clock input and output signals underneath the BGA package. The clock output signals should go directly outwards from the BGA footprint.

- 5. Avoid placing the OSC\_P and OSC\_N signals on the same layer as the clock outputs. Add grounded guard traces surrounding the OSC\_P and OSC\_N signals.

- 6. Where possible, place the CKOUT and CKIN signals on separate PCB layers with a ground layer between them. The use of ground guard traces between all clock inputs and outputs is recommended.

For more information, see the Si537x-EVB Evaluation Board User's Guide and Appendix I of the Si53xx Reference Manual, Rev 0.5 or higher.

# **5.2. Thermal Considerations**

The Si5374 dissipates a significant amount of heat and it is important to take this into consideration when designing the Si5374 operating environment. Among other issues, high die temperatures can result in increased jitter and decreased long term reliability. It is therefore recommended that one or more of the following occur:

- 1. Use a heat sink A heat sink example is Aavid part number 375324B00035G.

- 2. Use a Vdd voltage of 1.8 V.

- 3. Limit the ambient temperature to significantly less that 85 °C.

4. Implement very good air flow.

## 5.3. SCL Leakage

When selecting pull up resistors for the two l<sup>2</sup>C signals, note that there is an internal pull down resistor of 18 k $\Omega$  from the SCL pin to ground. This comment does not apply to the SDA pin.

## 5.4. RSTL\_x Pins

It is recommended that the four RSTL\_x pins (RSTL\_A, RSTL\_B, RSTL\_C and RSTL\_D) be logically connected together such that all four DSPLLs are either in or out of reset mode. When a DSPLL is in reset mode, its VCO will not be locked to any signal and may drift across its operating range. If a drifting VCO has a frequency similar to that of an operating VCO, there could be some crosstalk between the two VCOs. To avoid this from occurring during device initialization, DSPLLsim loads each DSPLL with default Free Run frequency plans with VCO values apart from one another. If the four RSTL\_x pins are directly connected to one another, the connections should not be made directly underneath the BGA package. Instead, the connections should be made outside the package footprint.

## 5.5. Reference Oscillator Selection

Care should be taken during the selection of the external oscillator that is connected to the OSC\_P and OSC\_N pins. There is no jitter attenuation from the OSC reference inputs to the output; so, to achieve low output jitter, a low-jitter reference OSC must be used. Also, the output drift during holdover will be the same as the drift of the OSC reference. For example, a Stratum 3 application will require an OSC reference source that has Stratum 3 stability (though Stratum 3 accuracy is not required).

The OSC frequency can be any value from 109 to 125.5 MHz. See the RATE\_REG (reg 2) description. Alternately, for applications with less demanding jitter requirements, the OSC frequency can be in the range from 37 to 41 MHz. For applications that use Free Run mode, the freedom to use any OSC frequency within these bands can be used to select an OSC frequency that has an integer relationship to the desired output frequency, which will make it easier to find a high-performance frequency plan.

If Free Run is not being used, an OSC frequency that is not integer-related to the output frequency is preferred. A recommended choice for an external oscillator is the Skyworks Solutions 530EB121M109DG, which is a 2.5 V, LVPECL device with a temperature stability of 20 ppm. It was used to take the typical phase noise plot on page 14. For more details and a more complete discussion of these topics, see the Si53xx Reference Manual. The very low loop BW of the Si5374 means that it can be susceptible to OSC\_P/OSC\_N reference sources that have high wander. Experience has shown that in spite of having low jitter, some MEMs oscillators have high wander, and these devices should be avoided. Skyworks Solutions does not recommend using MEMS based oscillators as the Si5374 frequency reference.

Contact Skyworks Solutions for details.

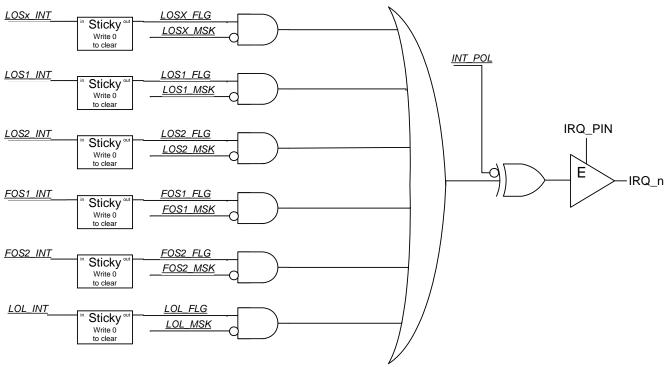

#### 5.6. Alarms

To assist in the programming of the IRQ\_n pins, refer to the below diagram of the Si5374 alarm structure.

Figure 5. Si5374 Alarm Structure

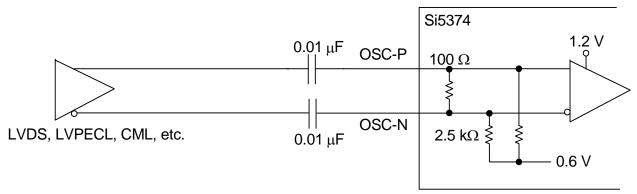

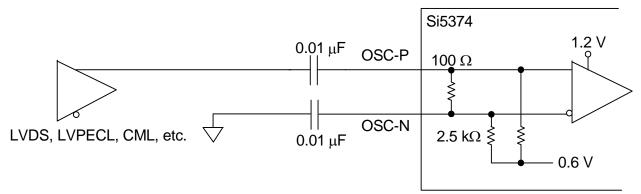

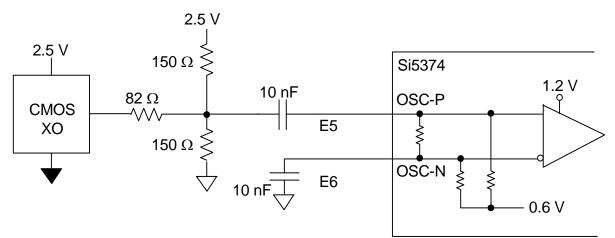

## 5.7. OSC\_P and OSC\_N Connection

Figures 6, 7, and 8 show examples of connecting various OSC reference sources to the OSC\_P and

OSC\_N pins. A crystal may not be used in place of an external oscillator.

Figure 6. Differential OSC Reference Input Example for Si5374

Figure 7. Single-Ended OSC Reference Input Example for Si5374

Figure 8. Single-Ended, 2.5 V, CMOS XO Connection

# 6. Register Map

The Si5374 has four identical register maps for each DSPLL. Each DSPLL has a unique I<sup>2</sup>C address enabling independent control and device configuration. The I<sup>2</sup>C address is 11010 [A1] [A0] for the entire device. Each corresponding DSPLL [A1] [A0] address is fixed as below.

|         | [A1] | [A0] |

|---------|------|------|

| DSPLLA: | 0    | 0    |

| DSPLLB: | 0    | 1    |

| DSPLLC: | 1    | 0    |

| DSPLLD: | 1    | 1    |

|         |      |      |

Note: The Si5374 register map is similar, but not identical, to the Si5324 device.

All register bits that are not defined in this map should always be written with the specific reset values. Writing to these bits with values other than the specified reset values may result in undefined device behavior. Registers not listed, such as Register 64, should never be written to.

| Reg. | D7                  | D6           | D5                  | D4         | D3              | D2          | D1                | D0        |

|------|---------------------|--------------|---------------------|------------|-----------------|-------------|-------------------|-----------|

| 0    |                     | FREE_RU<br>N | CKOUT_<br>ALWAYS_ON |            |                 |             | BYPASS_REG        |           |

| 1    |                     |              |                     |            | CK_PRI          | OR2[1:0]    | CK_PRI            | OR1[1:0]  |

| 2    |                     | BWSEL        | _REG[3:0]           |            |                 | RATE_       | REG [3:0]         |           |

| 3    | CKSEL_F             | REG[1:0]     | DHOLD               | SQ_ICAL    |                 |             |                   |           |

| 4    | AUTOSEL_REG[1:0]    |              |                     |            |                 | HIST_DEL[4: | 0]                |           |

| 5    | ICMOS               | S[1:0]       |                     |            |                 |             |                   |           |

| 6    |                     |              | S                   | FOUT2_REG[ | 2:0}            |             | SFOUT1_REG[2:0    | 0]        |

| 7    |                     |              |                     |            |                 |             | FOSREFSEL[2:0     | ]         |

| 8    | HLOG_               | _2[1:0]      | HLOG_               | _1[1:0]    |                 |             |                   |           |

| 9    |                     |              | HIST_AVG[4:0]       |            |                 |             |                   |           |

| 10   |                     |              |                     |            | DSBL2_REG       | DSBL1_REG   |                   |           |

| 11   |                     |              |                     |            |                 |             | PD_CK2            | PD_CK1    |

| 19   | FOS_EN FOS_THR[1:0] |              |                     | VALT       | IME[1:0]        |             | LOCKT[2:0]        |           |

| 20   |                     |              |                     |            | Write 0         | Write 0     | LOL_PIN           | IRQ_PIN   |

| 21   | Write 0             | Write 0      |                     |            |                 |             | CK1_ACT-<br>V_PIN | CKSEL_PIN |

| 22   |                     |              |                     |            | CK_ACTV_<br>POL |             | LOL_POL           | INT_POL   |

| 23   |                     |              |                     |            |                 | LOS2_MSK    | LOS1_MSK          | LOSX_MSK  |

| 24   |                     |              |                     |            |                 | FOS2_MSK    | FOS1_MSK          | LOL_MSK   |

| 25   |                     | N1_HS[2:0]   |                     |            |                 |             |                   |           |

| 31   |                     |              |                     |            |                 | NC1_L       | _S[19:16]         |           |

| 32   |                     | 1            |                     | ١          | NC1_LS[15:8]    |             |                   |           |

#### Table 8. Si5374 Registers

20 Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 1.1 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • March 14, 2022

## Table 8. Si5374 Registers (Continued)

| Reg. | D7      | D6               | D5               | D4               | D3            | D2       | D1                | D0                |  |  |  |