## Si47xx ANTENNA, SCHEMATIC, LAYOUT, AND DESIGN GUIDELINES

## 1. Introduction

This document provides general Si47xx design guidelines and AM/FM/SW/LW/WB antenna selections which includes schematic, BOM, layout and design checklist.

All users should follow the Si47xx design guidelines presented in Section 2 and then users can proceed to the appropriate antenna selections according to the application and device used presented in Sections 3 through 10.

To get an in-depth knowledge about each individual antenna, the antenna theory and interface model is presented in the Appendices.

| Part Number | Description                   | Function       |             |             | FM Antenna     |             | WB Antenna | A M/I W Antonna |       | SW Antenna |              |          |      |

|-------------|-------------------------------|----------------|-------------|-------------|----------------|-------------|------------|-----------------|-------|------------|--------------|----------|------|

|             |                               | FM Transmitter | FM Receiver | AM Receiver | SW/LW Receiver | WB Receiver | Headphone  | Embedded        | Cable | Whip       | Ferrite Loop | Air Loop | Whip |

| Si4700      | FM Receiver                   |                | ✓           |             |                |             | ✓          |                 |       |            |              |          |      |

| Si4701      | FM Receiver with RDS          |                | ✓           |             |                |             | ✓          |                 |       |            |              |          |      |

| Si4702      | FM Receiver                   |                | ✓           |             |                |             | ✓          |                 |       |            |              |          |      |

| Si4703      | FM Receiver with RDS          |                | ✓           |             |                |             | ✓          |                 |       |            |              |          |      |

| Si4704      | FM Receiver                   |                | ✓           |             |                |             | ✓          | ✓               | ✓     |            |              |          |      |

| Si4705      | FM Receiver with RDS          |                | ✓           |             |                |             | ✓          | ✓               | ✓     |            |              |          |      |

| Si4706      | High Performance RDS Receiver |                | ✓           |             |                |             | ✓          | ✓               | ✓     |            |              |          |      |

| Si4707      | WB Receiver with SAME         |                |             |             |                | ✓           |            |                 |       | ✓          |              |          |      |

| Si4710      | FM Transmitter                | $\checkmark$   |             |             |                |             |            | ✓               | ✓     |            |              |          |      |

| Si4711      | FM Transmitter with RDS       | $\checkmark$   |             |             |                |             |            | ✓               | ✓     |            |              |          |      |

| Si4712      | FM Transmitter with RPS       | ✓              |             |             |                |             |            | ✓               | ✓     |            |              |          |      |

| Si4713      | FM Transmitter with RDS & RPS | ✓              |             |             |                |             |            | ✓               | ✓     |            |              |          |      |

| Si4720      | FM Transceiver                | ✓              | ✓           |             |                |             | ✓          | ✓               | ✓     |            |              |          |      |

| Si4721      | FM Transceiver with RDS       | ✓              | ✓           |             |                |             | ✓          | ✓               | ✓     |            |              |          |      |

| Si4730      | AM/FM Receiver                |                | ✓           | ✓           |                |             | ✓          |                 |       |            | ✓            | ✓        |      |

| Si4731      | AM/FM Receiver with RDS       |                | ✓           | ✓           |                |             | ✓          |                 |       |            | ✓            | ✓        |      |

| Si4734      | AM/SW/LW/FM Receiver          |                | ✓           | ✓           | ✓              |             | ✓          |                 |       |            | ~            | ✓        | ✓    |

| Si4735      | AM/SW/LW/FM Receiver with RDS |                | ✓           | ✓           | ✓              |             | ✓          |                 |       |            | ✓            | ✓        | ✓    |

| Si4736      | AM/FM/WB Receiver             |                | ✓           | ✓           |                | ✓           | ✓          |                 |       | ✓          | ~            | ✓        |      |

| Si4737      | AM/FM/WB Receiver with RDS    |                | ✓           | ✓           |                | ✓           | ✓          |                 |       | ✓          | ✓            | ✓        |      |

| Si4738      | FM/WB Receiver                |                | ✓           |             |                | ✓           | ✓          |                 |       | ✓          |              |          |      |

| Si4739      | FM/WB Receiver with RDS       |                | ✓           |             |                | ✓           | ✓          |                 |       | ✓          |              |          |      |

| Si4784      | FM Receiver                   |                | ✓           |             |                |             | ✓          |                 | ✓     |            |              |          |      |

| Si4785      | FM Receiver with RDS          |                | ✓           |             |                |             | ✓          |                 | ✓     |            |              |          |      |

**Table 1. Supported Devices and Antennas**

2 Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

## TABLE OF CONTENTS

## Section Page 1. Introduction 2.4. Si47xx 3x3 mm Bill of Materials ......10 2.6. Si47xx 3x3 mm Design Checklist ......16 5. Embedded Antenna for FM Transmit on TXO and Receive on LPI 6. Cable Antenna for FM Transmit on TXO and Receive on LPI 8. Ferrite Loop Antenna for AM/LW Receive on AMI (Si4730/31/34/35/36/37 Only) .....39

| 8.1. Ferrite Loop Antenna Design                                          | 39 |

|---------------------------------------------------------------------------|----|

| 8.2. Ferrite Loop Antenna Schematic                                       | 40 |

| 8.3. Ferrite Loop Antenna Bill of Materials                               | 40 |

| 8.4. Ferrite Loop Antenna Layout                                          | 41 |

| 8.5. Ferrite Loop Antenna Design Checklist                                | 41 |

| 9. Air Loop Antenna for AM/LW Receive on AMI (Si4730/31/34/35/36/37 Only) | 42 |

| 9.1. Air Loop Antenna Design                                              | 42 |

| 9.2. Air Loop Antenna Schematic                                           | 43 |

| 9.3. Air Loop Antenna Bill of Materials                                   | 44 |

| 9.4. Air Loop Antenna Layout                                              | 44 |

| 9.5. Air Loop Antenna Design Checklist                                    | 44 |

| 10. Whip Antenna for SW Receive on AMI (Si4734/35 Only)                   | 45 |

| 10.1. SW Whip Antenna Design                                              | 45 |

| 10.2. SW Whip Antenna Schematic                                           | 46 |

| 10.3. SW Whip Antenna Bill of Materials                                   | 48 |

| 10.4. SW Whip Antenna Layout                                              | 49 |

| 10.5. SW Whip Antenna Design Checklist                                    | 49 |

| Appendix A—FM Receive Headphone Antenna Interface Model                   | 50 |

| Appendix B—FM Transmit Embedded Antenna Interface Model                   | 55 |

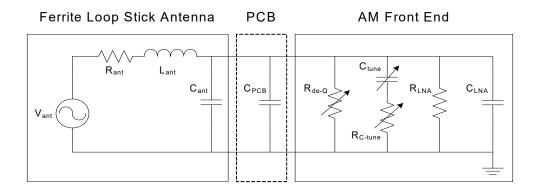

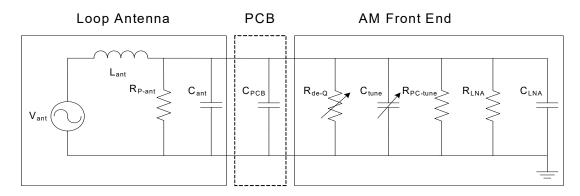

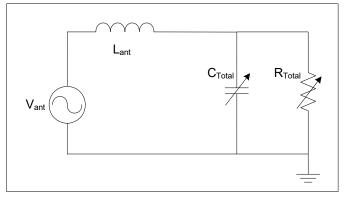

| Appendix C—AM Ferrite Loop Stick Antenna Interface Model                  | 63 |

| Document Change List                                                      | 67 |

| Contact Information                                                       | 68 |

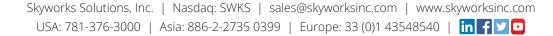

## 2. Si47xx 3x3 mm QFN Schematic and Layout

This section shows the minimal schematic and layout options required for optimal Si47xx performance. Population options are provided to support a single layout for all 3 x 3 mm QFN devices, mitigate system noise, operate the internal oscillator with an external crystal, and filter VCO energy.

## 2.1. Si47xx 3x3 mm Design

C1 (22 nF) is a required bypass capacitor for VD/VDD supply pin 11. Place C1 as close as possible to the VD/VDD pin 11 and GND pin 12. Place a via connecting C1 VD/VDD supply to the power rail such that the cap is closer to the Si47xx than the via. Route C1 GND directly and only to GND pin 12 with a wide, low inductance trace. C1 GND should not be routed to GND via. These recommendations are made to reduce the size of the current loop created by the bypass cap and routing, minimize bypass cap impedance and return all currents to the GND pad.

Note: For Si47xx rev D parts, C1 is required on pin 11 (VA). The C1 design guidelines described above should be followed. For an illustration of these guidelines, refer to Figure 3.

C2 (22 nF) is an optional bypass capacitor for VA/LIN/DFS supply pin 16 (Si4702/03 only) and may be placed to mitigate supply noise. Place C2 as close as possible to the VA/LIN/DFS pin 16 and GND pin 15. Place a via connecting C2 VA supply to the power rail such that the cap is closer to the Si47xx than the via. Route C2 GND directly and only to GND pin 15 with a wide, low inductance trace. Route GND/RIN/DOUT pin 15 to the GND pad if designing only for the Si4702/03. If designing for all Si47xx devices, do not route GND/RIN/DOUT pin 15 to the GND pad. In this case the on-chip connection between pin 15 and the GND pad will provide a ground connection. These recommendations are made to reduce the size of the current loop created by the bypass cap and routing, minimize bypass cap impedance and return all currents to the GND pad.

C3 (100 nF) is an optional bypass capacitor for the VIO supply pin 10 and may be placed to mitigate supply noise. Place C3 as close as possible to the VIO pin 10 and the GND pin 12. Place a via connecting C3 VIO supply to the power rail such that the cap is closer to the Si47xx than the via. Route C3 GND directly and only to GND pin 12 with a wide, low inductance trace. C3 GND should not be routed to GND via. These recommendations are made to reduce the size of the current loop created by the bypass cap and routing, minimize bypass cap impedance and return all currents to the GND pad.

**Note:** For Si47xx rev D parts, C3 is required on pin 10 (VD). The C3 design guidelines described above should be followed. C6 and C7 ( $0.39\mu$ F) are ac coupling caps for transmitter audio input to VA/LIN/DFS pin 16 and GND/RIN/DOUT pin 15 (Si471x/2x analog audio input mode only). The input resistance of the transmitter audio input and the cap will set the high pass pole given by Equation 1. The input resistance of the audio input is programmatically selectable as 396 k $\Omega$ , 100 k $\Omega$ , 74 k $\Omega$ , or 60 k $\Omega$  (default). Placement location is not critical.

$$f_c = \frac{1}{2\pi RC}$$

#### **Equation 1. High-Pass Pole Calculation**

C8 and C9 (0.39  $\mu$ F.) are ac coupling caps for receiver analog audio output from ROUT/DIN pin 13 and LOUT/DFS pin 14 (Si470x/2x/3x/8x audio output mode only). The input resistance of the amplifier, such as a headphone amplifier, and the capacitor will determine the high pass pole given by Equation 1. Placement location is not critical.

C10 and C11 (7–22 pF) are optional crystal loading caps required only when using the internal oscillator feature. Refer to the crystal data sheet for the proper load capacitance and be certain to account for parasitic capacitance. Place caps C10 and C11 such that they share a common GND connection and the current loop area of the crystal and loading caps is minimized.

C12 and C13 (2.2 pF) are noise mitigation caps if digital audio option is in use. The caps need to be placed close to the Si47xx chip.

X1 (32.768 kHz) is an optional crystal required only when using the internal oscillator feature. Place the crystal X1 as close to GPO3/DCLK pin 17 and RCLK pin 9 as possible to minimize current loops. Route the RCLK trace as far from SDIO pin 8 and SDIO trace as possible to minimize capacitive coupling.

R1 (0  $\Omega$ ) is an optional jumper used to route the digital audio clock to GPO3/DCLK pin 17. R1 is only required for a universal design which accommodates BOM population options selecting between crystal and digital audio (Si4705/06/1x/2x/31/35/37/39/8x only).

## AN383

Note: Crystal and digital audio mode cannot be used at the same time. Populate R1 and remove C10, C11, and X1 when using digital audio.

Populate C10, C11, and X1 and remove R1 when using the internal oscillator. Place resistor R1 as close to DCLK/GPO3 pin 17 as possible as shown in Layout Example 4 to minimize trace length from pin 17 to the crystal and load cap.

R2-R6  $(25 \Omega - 2 k\Omega)$  are optional series termination resistors and are used to mitigate system noise. The recommended value of the resistors is  $2 k\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place the series termination resistors R2-R6 as close to the host controller as possible.

R7 and R8 (4.7 k $\Omega$ ) are optional pull-up resistors for the SCLK and SDIO lines required only when using an I<sup>2</sup>C bus. The size of pull-up resistor value will vary based on the number of devices, capacitance and speed of the bus. Placement location is not critical. Refer to the I<sup>2</sup>C specification for additional design information.

R9 (0  $\Omega$ ) is used to route power to VA/LIN/DFS supply pin 16. R9 is only required to support a layout for all 3x3 mm QFN devices. If designing for the Si4702/03 only R9 may be replaced with trace connections. If designing for Si4704/05/06/07/1x/2x/3x/8x only, R9 is not required. Place resistor R9 as close to VA/LIN/DFS pin 16 as possible. R10 (0  $\Omega$ ) is an optional jumper used to route the VA pin 16 for Si4702/03. R10 is only required for a universal design which supports BOM options for the Si4702/03 and other Si47xx devices. R10 should be populated when using an Si4702/03 and not populated when using an alternate device.

R11 (0  $\Omega$ ) is an optional jumper used to route the DFS to VA/LIN/DFS pin 16. R11 is only required for a design in which the Si4702/03 and digital audio output (Si4705/06/21/31/35/37/39/8x) BOM options are desired. Place resistor R11 as close to pin VA/LIN/DFS 16 as possible.

R12  $(25 \Omega - 2 k\Omega)$  is a required series termination resistor when using digital audio output (Si4705/06/21/31/35/37/39/8x) and is used to mitigate noise from the digital data routed from GND/RIN/DOUT pin 15. The recommended value of the resistor is 604  $\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place R12 as close to pin 15 as possible.

R13 (25  $\Omega$ –2 k $\Omega$ ) is a required series termination resistor when using digital audio (Si4705/06/1x/2x/31/35/37/39/8x only) and is used to mitigate noise from the digital clock routed to GPO3/DCLK pin 17. The recommended value of the resistor is 2 k $\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place R13 as close to the host controller as possible.

R14  $(25 \Omega - 2 k\Omega)$  is a required series termination resistor when using digital audio output (Si4705/06/21/31/35/37/39/8x) and is used to mitigate noise from the digital frame clock routed to VA/LIN/DFS pin 16. The recommended value of the resistor is 2 k $\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place R14 as close to the host controller as possible.

R15 ( $25 \Omega - 2 k\Omega$ ) is a required series termination resistor when using digital audio input (Si471x/2x only) and is used to mitigate noise from the digital frame clock routed to LOUT/DFS pin 14. The recommended value of the resistor is 2 k $\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place R15 as close to the host controller as possible.

R16 ( $25 \Omega - 2 k\Omega$ ) is a required series termination resistor when using digital audio input (Si471x/2x only) and is used to mitigate noise from the digital data routed to ROUT/DIN pin 13. The recommended value of the resistors is  $2 k\Omega$  for optimal edge rate and noise suppression. Confirm that timing requirements are met with the selected series termination resistor value. Place R16 as close to the host controller as possible.

R17 (0  $\Omega$ ) is an optional jumper used to route the GND pin 15 for Si4702/03. R17 is only required for a universal design which supports BOM options for the Si4702/03 and other Si47xx devices. R17 should be populated when using an Si4702/03 and not populated when using an alternate device. Place R17 as close to the Si47xx as possible.

R18 (0  $\Omega$ ) is an optional jumper used to route the GND pin 4 for Si4702/03. R18 is only required for a universal design which supports BOM options for the Si4702/03 and other Si47xx devices. R18 should be populated when using an Si4702/03 and not populated when using an alternate device. Place R18 as close to the Si47xx as possible.

<sup>6</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

## 2.2. Emissions Mitigation Components

The following components may be placed to reduce VCO emissions. This is only required if regulatory testing requires measuring emissions at the VCO frequency of 3–4 GHz. Refer to Section "2.6.1. Emissions Mitigation Checklist" for detailed layout and grounding recommendations pertaining to the components described below.

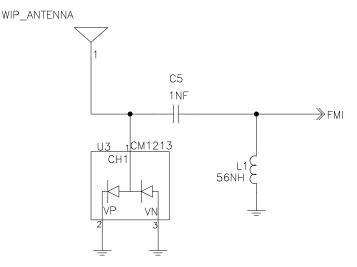

#### 2.2.1. FMI Mitigation Components

| Option | Components                                  | Sensitivity                   | Mitigation | Cost   |

|--------|---------------------------------------------|-------------------------------|------------|--------|

| 1      | C5 = NP<br>F1 = BLM15GA750SN1<br>C14 = 6 pF | Best                          | Best       | Higher |

| 2      | C5 = 2.7 pF<br>F1 = 20 nH<br>C14 = 2.7 pF   | Less<br>(+1.75 dB vs Option1) | Good       | Lower  |

## **Table 2. FMI Mitigation Components**

C5 (NP) is an optional filter capacitor for FMI pin 2 and may be placed to shunt VCO energy to GND and prevent it from radiating from an antenna connected to the FMI pin. This pad is a placeholder for alternate emission mitigation option 2. While it is recommended to select option 1 for best sensitivity and mitigation performance, leaving this pad ensures that there is no redesign necessary between options. Route pin 2 to GND/RFGND if the pin functionality is not used.

F1 (BLM15GA750SN1) is an optional bead for FMI pin 2 and may be placed to prevent VCO energy from radiating from FMI pin. Place F1 as close as possible to FMI pin 2. Route pin 2 to GND/RFGND if the pin functionality is not used.

C14 (6 pF) is an optional filter capacitor for FMI pin 2 and may be placed to shunt VCO energy to GND and prevent it from radiating from an antenna connected to the FMI pin. Place C14 as close as possible to FMI pin 2. The ground path should be optimized on the top layer. Route pin 2 to GND/RFGND if the pin functionality is not used.

#### 2.2.2. AMI Mitigation Components

## **Table 3. AMI Mitigation Components**

| Option | Components                                 | Sensitivity                 | Mitigation | Cost   |

|--------|--------------------------------------------|-----------------------------|------------|--------|

| 1      | C17 = 3.3 pF<br>L2 = 10 nH<br>C16 = 3.3 pF | Best                        | Good       | Lower  |

| 2      | C17 = 2.7 pF<br>L2 = 20 nH<br>C16 = 2.7 pF | Less<br>(+3 dB vs Option1)  | Better     | Lower  |

| 3      | C17 = NP<br>L2 = BLM15GA750SN1<br>C16 = NP | Least<br>(+6 dB vs Option1) | Best       | Higher |

C17 (3.3 pF) is an optional filter capacitor for AMI pin 4 on Si473x devices and may be placed to shunt VCO energy to GND and prevent it from radiating from an antenna connected to the AMI pin. Place C17 as close as possible to AMI pin 4 and RFGND pin 3. The ground path should be optimized on the top layer. Route pin 4 to GND/RFGND if the pin functionality is not used.

L2 (10 nH) is an optional filter inductor for AMI pin 4 on Si473x devices and may be placed to prevent VCO energy from radiating from AMI pin. Place L2 as close as possible to AMI pin 4. Route pin 4 to GND/RFGND if the pin functionality is not used.

C16 (3.3 pF) is an optional filter capacitor for AMI pin 4 on Si473x devices and may be placed to shunt VCO energy to GND and prevent it from radiating from an antenna connected to the AMI pin. Place C16 as close as possible to AMI pin 4 and RFGND pin 3. The ground path should be optimized on the top layer. Route pin 4 to GND/RFGND if the pin functionality is not used.

#### 2.2.3. GPIO Mitigation Components

| Option | Components                                               | Sensitivity | Mitigation | Cost |

|--------|----------------------------------------------------------|-------------|------------|------|

| 1      | C15 = 33 pF<br>R20 = 330 Ω<br>C18 = 33 pF<br>R19 = 330 Ω | Best        | Best       | Low  |

| 2      | C15 = 33 pF<br>R20 = 330 Ω<br>C18 = NP<br>R19 = 330 Ω    | Best        | Good       | Low  |

## **Table 4. GPIO Mitigation Components**

C15 (33 pF) is an optional filter capacitor for GPO1 pin 19 and may be placed to shunt VCO energy to GND and prevent it from radiating. Place C15 as close as possible to GPO1 pin 19. The ground path should be optimized on the top layer.

R20 (330  $\Omega$ ) is an optional mitigating resistor for GPO1 pin 19 and may be placed to prevent VCO energy from radiating from GPO1 pin. Place R20 as close as possible to GPO1 pin 19. R20 is not required if GPO1 is pulled up/down by design and has no other connections.

C18 (33 pF) is an optional filter capacitor for GPO2 pin 18 and may be placed to shunt VCO energy to GND and prevent it from radiating. Place C18 as close as possible to GPO2 pin 18. The ground path should be optimized on the top layer.

R19 (330  $\Omega$ ) is an optional mitigating resistor for GPO2 pin 18 and may be placed to prevent VCO energy from radiating from GPO2 pin. Place R19 as close as possible to GPO2 pin 18. R19 is not required if GPO2 is pulled up/down by design and has no other connections.

## 2.2.4. LPI Mitigation Components

| Table 5. LPI Mitig | gation Components |

|--------------------|-------------------|

|--------------------|-------------------|

| Option | Components                | Sensitivity | Mitigation | Cost |

|--------|---------------------------|-------------|------------|------|

| 1      | C4 = 3.3 pF<br>L1 = 15 nH | Best        | Best       | Low  |

C4 (3.3 pF) is an optional filter capacitor for TXO/LPI pin 4 on Si4704/05/06/1x/2x devices and may be placed to shunt VCO energy to GND and prevent it from radiating from an antenna connected to the TXO/LPI pin. Make measurements with different C4 and L1 values in-system to optimize the filter's performance for the antenna design chosen. Place C4 as close as possible to TXO/LPI pin 4 and RFGND pin 3. The ground path should be optimized on the top layer. Route pin 4 to GND/RFGND if the pin functionality is not used.

L1 (15 nH) is an optional filter inductor for TXO/LPI pin 4 on Si4704/05/06/1x/2x devices and may be placed to prevent VCO energy from radiating from an antenna connected to the TXO/LPI pin. Make measurements with different C4 and L1 values in-system to optimize the filter's performance for the antenna design chosen. Place L1 as close as possible to TXO/LPI pin 4. Route pin 4 to GND/RFGND if the pin functionality is not used.

<sup>8</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

## 2.3. Si47xx 3x3 mm Schematic

Figure 1. Si47xx 3x3 mm QFN Schematic

## 2.4. Si47xx 3x3 mm Bill of Materials

The required bill of materials for Figure 1 is shown in Table 6.

#### Table 6. Required Bill of Materials

| Designator | Description                                               | Note                                                                                                                    |

|------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| C1         | VD/VDD Supply bypass capacitor,<br>22 nF, 10%, Z5U/X7R    |                                                                                                                         |

| C3         | VI0 Supply bypass capacitor,<br>100 nF, 10%, Z5U/X7R      | For supply noise mitigation.<br>Optional for Si47xx rev C and earlier parts.<br>For Si47xx rev D parts, C3 is required. |

| R12        | DOUT current limiting resistor, 604 $\Omega$              | For digital audio output<br>(Si4705/06/21/31/35/37/39/8x only)                                                          |

| R13        | DCLK current limiting resistor, 25 $\Omega$ –2 k $\Omega$ | For digital audio<br>(Si4705/06/1x/2x/31/35/37/39/8x only)                                                              |

| R14        | DFS current limiting resistor, 25 $\Omega$ –2 k $\Omega$  | For digital audio output<br>(Si4705/06/21/31/35/37/39/8x only)                                                          |

| R15        | DFS current limiting resistor, 25 $\Omega$ –2 k $\Omega$  | For digital audio input (Si471x/2x only)                                                                                |

| R16        | DIN current limiting resistor, 25 $\Omega2$ k $\Omega$    | For digital audio input (Si471x/2x only)                                                                                |

| U1         | Skyworks Solutions Si47xx,<br>3x3 mm, 20 pin, QFN         |                                                                                                                         |

The optional bill of materials for Figure 1 is shown in Table 7.

## Table 7. Optional Bill of Materials

| Designator                               | Description                                        | Note                                                 |  |  |

|------------------------------------------|----------------------------------------------------|------------------------------------------------------|--|--|

| C2                                       | VA Supply bypass capacitor,<br>22 nF, 10%, Z5U/X7R | For supply noise mitigation (Si4702/03 only)         |  |  |

| C6, C7                                   | AC coupling capacitor,<br>0.39 µF, X7R/X5R         | For analog audio input<br>(Si471x/2x only)           |  |  |

| C8, C9                                   | AC coupling capacitor,<br>0.39 μF, X7R/X5R         | For analog audio output                              |  |  |

| C10, C11                                 | Crystal load capacitor, 22 pF, 5%, C0G             | For internal oscillator option                       |  |  |

| C12, C13                                 | Noise mitigation capacitor<br>2.2 pF, C0G          | For DFS noise mitigation purpose                     |  |  |

| R2–R6                                    | Current limiting resistor, 25–2 k $\Omega$         | For digital system noise mitigation                  |  |  |

| R7,R8                                    | Pullup resistor, 4.7 k $\Omega$                    | For I <sup>2</sup> C bus mode communication          |  |  |

| R1, R9, R10, R11,<br>R17, R18 0 Ω jumper |                                                    | For universal layout design supporting all<br>Si47xx |  |  |

| X1                                       | Crystal, Epson FC-135                              | For internal oscillator feature                      |  |  |

<sup>10</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

| Designator | Description                                           | Note                                                       |

|------------|-------------------------------------------------------|------------------------------------------------------------|

| C4         | VCO filter capacitor<br>3.3 pF, 0402, C0G             | For filtering of VCO energy<br>(Si4704/05/06/1x/2x only)   |

| C5         | VCO filter capacitor<br>NP, 0402, C0G                 | Placeholder pad for alternate FMI VCO filter configuration |

| C14        | VCO filter capacitor<br>6 pF, 0402, C0G               | For filtering of VCO energy                                |

| C15, C18   | VCO filter capacitor<br>33 pF, 0402, C0G              | For filtering of VCO energy                                |

| C16, C17   | VCO filter capacitor<br>3.3 pF, 0402, C0G             | For filtering of VCO energy<br>(Si473x only)               |

| F1         | VCO filter bead<br>Murata BLM15GA750SN1               | For filtering of VCO energy                                |

| L1         | VCO filter inductor<br>15 nH (Murata LQW18ANR15NJ00D) | For filtering of VCO energy<br>(Si4704/05/06/1x/2x only)   |

| L2         | VCO filter inductor<br>10 nH (Murata LQW18AN10NJ00D)  | For filtering of VCO energy<br>(Si473x only)               |

| R19, R20   | VCO mitigating resistor,<br>330 Ω, 0402               | For filtering of VCO energy                                |

| Table 8. | <b>Optional Bill</b> | of Materials: | Emissions | Mitigation |

|----------|----------------------|---------------|-----------|------------|

|----------|----------------------|---------------|-----------|------------|

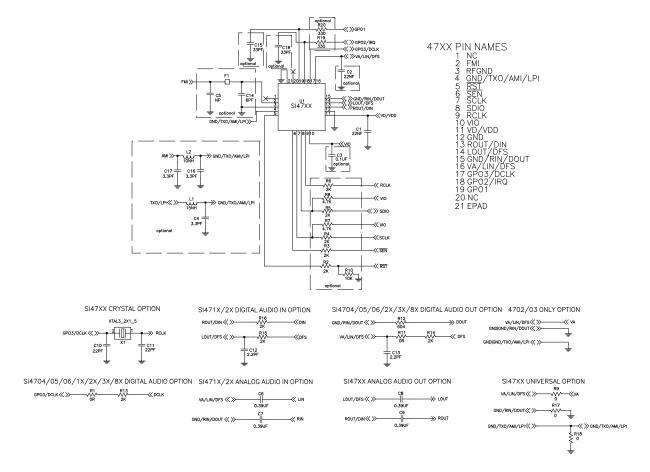

## 2.5. Si47xx 3x3 mm Layout

The following layout example selector guide provides guidance for selecting the proper example based on placement, routing, option, and device requirements. Layout examples 1, 2, and 3 show the critical component layout of the most common layout configurations. Layout example 4 shows a universal layout which supports all 3x3 mm QFN devices and features.

| Placement and Routing     |   | Layout Example |   |   |  |

|---------------------------|---|----------------|---|---|--|

|                           | 1 | 2              | 3 | 4 |  |

| Top Side Routing          | Х | х              | Х | Х |  |

| Inner/Bottom Side Routing | Х | х              | Х | Х |  |

| Top Side Placement        | Х | х              | Х | Х |  |

| Bottom Side Placement     |   | х              |   | Х |  |

Table 9. Layout Example Selector Guide by Place and Route Requirements

## Table 10. Layout Example Selector Guide by Option

| Feature        |   | Layout Example |   |   |

|----------------|---|----------------|---|---|

|                | 1 | 2              | 3 | 4 |

| Crystal        | Х | х              |   | Х |

| Analog Input   |   |                | х | Х |

| Analog Output  | Х | х              | х | Х |

| Digital Input  |   |                | Х | Х |

| Digital Output |   |                | Х | Х |

#### Table 11. Layout Example Selector Guide by Device

| Device          |   | Layout Example |   |   |

|-----------------|---|----------------|---|---|

|                 | 1 | 2              | 3 | 4 |

| Si4702/03       | X | Х              |   | Х |

| Si4704/05/06/07 | Х | Х              | Х | Х |

| Si471x          |   |                | Х | х |

| Si472x          | Х | Х              | Х | х |

| Si473x          | Х | Х              | х | х |

| Si478x          | X | Х              | х | х |

<sup>12</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

The following layout rules are used:

- Layer 1 top side placement and routing (shown)

- Layer 2 GND (not shown)

- Power routed by trace (not shown)

- 0402 component size or larger

- 6 mil traces

- 6 mil trace spacing

- 15 mil component spacing

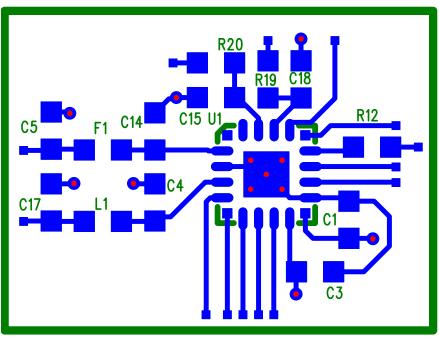

Figure 2 shows critical component layout with top side placement, top and bottom side routing, crystal and analog output support, and support for all devices except the Si471x transmitter family. The Si471x transmitter family can be supported in this example if VA bypass cap C2 is removed and audio input is routed to pin 15 and pin 16. Digital audio is not available when the crystal is used due to the multipurpose role of GPO3/DCLK pin 17. VIO bypass cap C3 is not included in this example in order to optimize routing of the crystal oscillator. Route the RCLK trace as far from the SDIO pin 8 and trace as possible by routing the SDIO trace on the bottom layer. If bottom side placement is possible, Figure 3 is preferred for optimal oscillator performance.

F1, C14, C15, C18, R19 and R20 are placed as close to the chip as possible. For the Si4704/05/06/2x with the short antenna option, pin 4 is populated with L1 and C4, C17 is not populated; for the Si473x AM receiver, C4 is replaced with C16, L1 is replaced with L2, and C17 is populated.

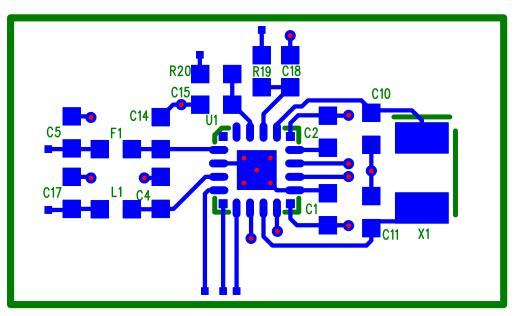

Figure 2. Layout Example 1

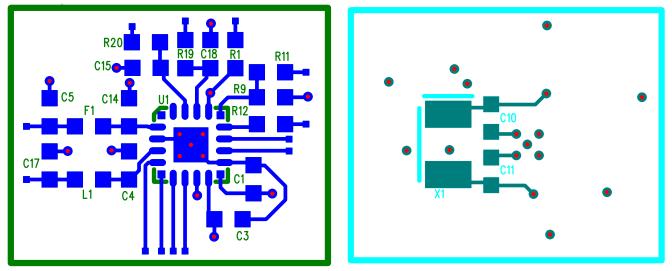

Figure 3 shows critical component layout with top and bottom side placement, top and bottom side routing, crystal and analog output support, and support for all devices except the Si471x transmitter family. The Si471x transmitter family can be supported in this example if VA bypass cap C2 is removed and audio input is routed to GND/RIN/DOUT pin 15 and VA/LIN/DFS pin 16. Digital audio is not available when the crystal is used due to the multipurpose role of GPO3/DCLK pin 17. Route the RCLK trace as far from the SDIO pin 8 and trace as possible by routing the RCLK trace on the bottom layer. This example is preferred for optimal oscillator performance.

F1, C14, C15, C18, R19, and R20 are placed as close to the chip as possible. For the Si4704/05/06/2x with the short antenna option, pin 4 is populated with L1 and C4, C17 is not populated; for the Si473x AM receiver, C4 is replaced with C16, L1 is replaced with L2, and C17 is populated.

Figure 3. Layout Example 2

Figure 4 shows critical component layout with top and bottom side placement, top and bottom side routing, analog and digital input and output support, and support for all devices except the Si4702/03 receiver family. The Si4702/03 receiver family can be supported in this example if the VA supply is routed to VA/LIN/DFS pin 16 and R12 is removed. The crystal is not available when digital audio is used due to the multipurpose role of GPO3/DCLK pin 17. Note that the RCLK trace is not a sensitive node when an external reference clock is used instead of the crystal. For this reason, an external reference clock allows more routing flexibility.

F1, C14, C15, C18, R19, and R20 are placed as close to the chip as possible. For the Si4704/05/06/2x with the short antenna option, pin 4 is populated with L1 and C4, C17 is not populated; for the Si473x AM receiver, C4 is replaced with C16, L1 is replaced with L2, and C17 is populated.

Figure 4. Layout Example 3

Figure 5 shows critical component layout with top and bottom side placement, top and bottom side routing, crystal support, analog and digital input and output support, and support for all devices. For this reason it is referred to as a universal layout. Either crystal or digital audio operation must be selected due to the multipurpose role of GPO3/DCLK pin 17. Note that the RCLK trace is not a sensitive node when an external reference clock is used instead of the crystal. For this reason, an external reference clock allows more routing flexibility. To support the crystal oscillator feature, route the RCLK trace as far from the SDIO pin 8 and trace as possible by routing the RCLK trace on the bottom layer.

F1, C14, C15, C18, R19 and R20 are placed as close to the chip as possible. For the Si4704/05/06/2x with the short antenna option, pin 4 is populated with L1 and C4, C17 is not populated; for the Si473x AM receiver, C4 is replaced with C16, L1 is replaced with L2, and C17 is populated.

Figure 5. Layout Example 4

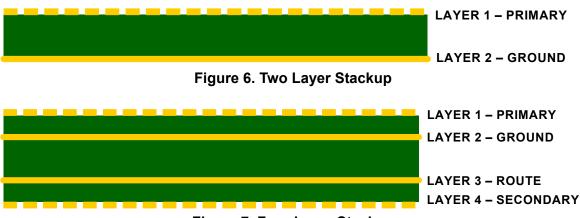

Place a ground plane under the Si47xx as shown in Figure 6, "Two Layer Stackup" or Figure 7, "Four Layer Stackup". For designs in which a continuous ground plane is not possible, place a local ground plane directly under the Si47xx. Do not route signal traces on the ground layer under the Si47xx and do not route signal traces under the Si47xx without a ground plane between the Si47xx and signal trace. Flood the primary and secondary layers with ground and place stitching vias to create a low impedance connection between planes.

Do not route digital or RF traces over breaks in the ground plane. Route all traces to minimize inductive and capacitive coupling by keeping digital traces away from analog and RF traces, minimizing trace length, minimizing parallel trace runs, and keeping current loops small. In particular, care should be taken to avoid routing digital signals or reference clock traces near or parallel to the VCO pins 1, 20 or LOUT/ROUT pins 14, 13. Digital traces should be routed in between ground planes (on the inner layers) for best performance. If that is not possible, route digital traces on the opposite side of the chip.

Route all GND (including RFGND) pins to the ground pad. The ground pad should be connected to the ground plane using multiple vias to minimize ground potential differences. The exception is GND/RIN/DOUT when designing for a universal layout.

Route power to the Si47xx by trace, ensuring that each trace is rated to handle the required current. Some trace impedance is preferable so that the decoupling currents are forced to flow through decoupling caps C1, C2, and C3 directly to the ground pins and not by alternate pathways.

Place the Si47xx close to the antenna(s) to minimize antenna trace length and capacitance and to minimize inductive and capacitive coupling. This recommendation must be followed for optimal device performance. Route the antenna trace over an unobstructed ground plane to minimize antenna loop area and inductive coupling. Design, Place, and Route other circuits such that radiation in the band of interest is minimized.

Figure 7. Four Layer Stackup

## 2.6. Si47xx 3x3 mm Design Checklist

The following design checklist summarizes the guidelines presented in this section:

- □ Place bypass caps C1, C2 and C3 as close as possible to the supply and ground pins.

- □ Place a via connecting C1, C2, and C3 to the power supplies such that the cap is between the Si47xx and the via.

- □ Route a wide, low inductance return current path from the C1, C2, and C3 to the Si47xx GND pins.

- □ Route GND/LIN/DOUT pin 15 to the GND pad if designing only for the Si4702/03.

- □ Route C1 GND directly and only to GND pin 12. Do not connect GND via to C1.

- □ Place resistor R1 as close to pin GPO3/DCLK 17 as possible.

- □ Place R9 as close as possible to VA/LIN/DFS pin16 as possible.

- □ Place resistor R11 as close to pin VA/LIN/DFS 16 as possible.

- □ Place resistor R12 as close to pin GND/RIN/DOUT 15 as possible.

- □ Place the series termination resistors R2–R6, R13–R16 as close to the host controller as possible.

- □ Place caps C12 or C13 close to the chip if digital audio is used.

- □ Place the crystal X1 as close to GPO3/DCLK pin 17 and RCLK pin 9 as possible.

- □ Route the SDIO trace and RCLK trace as far away from each other as possible when using crystal X1.

- □ Place caps C10 and C11 such that they share a common GND connection.

- □ Place a ground plane under the device as shown in Figure 6, "Two Layer Stackup" or Figure 7, "Four Layer Stackup".

- Place a local ground plane directly under the device for designs in which a continuous ground plane is not possible.

- Route all traces to minimize inductive and capacitive coupling by keeping digital traces away from analog and RF traces, minimizing trace length, minimizing parallel trace runs, and keeping current loops small.

- □ Route digital traces in between ground plane for best performance. If that is not possible, route digital traces on the opposite side of the chip.

- □ Route all GND (including RFGND) pins to the ground pad. The ground pad should be connected to the ground plane using multiple vias minimize ground potential differences. The exception is GND/RIN/DOUT when designing for the universal layout.

- □ Route power to the Si47xx by trace, ensuring that each trace is rated to handle the required current.

- Do not route signal traces on the ground layer directly under the Si47xx.

- Do not route signal traces under the Si47xx without a ground plane between the Si47xx and signal trace.

- Do not route digital or RF traces over breaks in the ground plane.

- □ Do not route digital signals or reference clock traces near to the VCO pin 1 and 20 or the LOUT/ROUT output pin 14 and 13.

- Do not route VCO pin 1 and 20 (NC). These pins must be left floating to guarantee proper operation.

- □ Place the Si47xx close to the antenna(s) to minimize antenna trace length and capacitance and to minimize inductive and capacitive coupling. This recommendation must be followed for optimal device performance.

- □ Route the antenna trace over an unobstructed ground plane to minimize antenna loop area and inductive coupling.

- Design, place, and route other circuits such that radiation in the band of interest is minimized.

- □ Tie unused pin(s) to GND, but do not tie No Connect (NC) pins to GND. For example, in Si471x FM transmitter analog audio input mode, DFS pin 14 and DIN pin 13 are not used; therefore, these two pins should be tied to GND.

#### 2.6.1. Emissions Mitigation Checklist

The following design checklist summarizes the guidelines for mitigating emissions in the 3–4 GHz range, if applicable.

- □ Place F1 as close as possible to FMI pin 2.

- □ Place C14 as close as possible to FMI pin 2.

- □ Place C5 even though it is designated as NP, it should be as close as possible to FMI pin2.

- □ On the Si4704/05/06/1x/2x products:

- Place C4 as close as possible to LPI/TXO pin 4 and RFGND pin 3.

- Place L1 as close as possible to LPI/TXO pin 4.

- □ On Si473x products:

- Place C16 as close as possible to AMI pin 4 and RFGND pin 3.

- Place L2 as close as possible to AMI pin 4.

- Place C17 as close as possible to AMI pin 4 and RFGND pin 3.

- Place C15 and C18 as close as possible to GPO1 & GPO2 pins.

- □ Place R19 and R20 as close as possible to GPO1 & GPO2 pins.

- □ Route FMI pin 2 to GND/RFGND if the pin functionality is not used.

- □ Route TXO/AMI/LPI pin 4 to GND/RFGND if the pin functionality is not used.

- □ Flood the primary and secondary layers with ground and place stitching vias between the GND fill and GND plane.

- □ Shunt capacitors C4, C5, C14, C15, C16, C17, and C18 should be connected directly to the GND plane on top layer.

- Do not use heat relief for these pad's GND connection.

- □ Connecting shunt capacitors only to a via to the GND plane is not sufficient; though it is permissible to have such a via if the top GND plane is also connected.

- □ If additional space is available, increase the size of RFGND trace by moving FMI and AMI signal paths further apart.

- □ Avoid unnecessary breaks in the top ground fill between the Si47xx and the system GND connection. The goal is to have the path from shunt capacitors as direct, unbroken, and wide as possible.

- □ Rotate the Si47xx (as necessary) in order to create the best ground path for the FMI and GPO mitigation as these are the greater contributors to emissions.

- □ Orient the shunt capacitor(s) on FMI (C14) to the right of the trace (towards pin 1).

- □ Orient the shunt capacitors on AMI (C16 & C17) to the right of the trace (toward RFGND, pin 3).

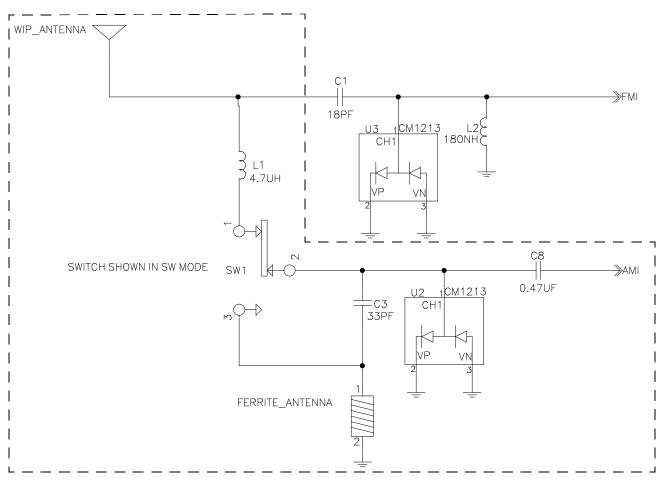

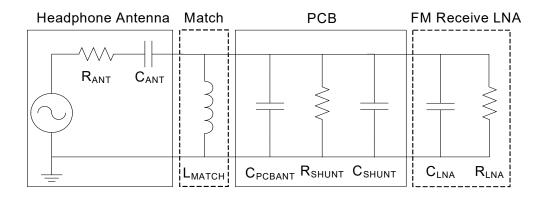

## 3. Headphone Antenna for FM Receiver on FMI (Si470x/2x/3x/8x Only)

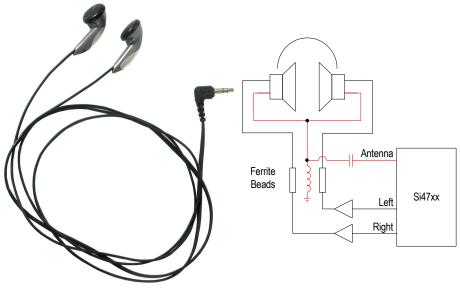

The Si470x/2x/3x FM Receiver component supports a headphone antenna interface through the FMI pin. A headphone antenna with a length between 1.1 and 1.45 m suits the FM application very well because it is approximately half the FM wavelength (FM wavelength is  $\sim$ 3 m).

## 3.1. Headphone Antenna Design

A typical headphone cable will contain three or more conductors. The left and right audio channels are driven by a headphone amplifier onto left and right audio conductors and the common audio conductor is used for the audio return path and FM antenna. Additional conductors may be used for microphone audio, switching, or other functions, and in some applications the FM antenna will be a separate conductor within the cable. A representation of a typical application is shown in Figure 8, "Typical Headphone Antenna Application".

Figure 8. Typical Headphone Antenna Application

## 3.2. Headphone Antenna Schematic

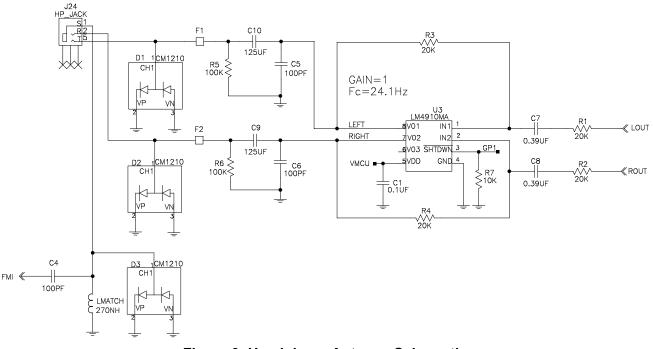

#### Figure 9. Headphone Antenna Schematic

The headphone antenna implementation requires components L<sub>MATCH</sub>, C4, F1, and F2 for a minimal implementation. The ESD protection diodes and headphone amplifier components are system components that will be required for proper implementation of any tuner.

Inductor  $L_{MATCH}$  is selected to maximize the voltage gain across the FM band.  $L_{MATCH}$  should be selected with a Q of 15 or greater at 100 MHz and minimal dc resistance.

AC-coupling capacitor C4 is used to remove a dc offset on the FMI input. This capacitor must be chosen to be large enough to cause negligible loss with an LNA input capacitance of 4–6 pF. The recommended value is 100 pF–1 nF.

Ferrite beads F1 and F2 provide a low-impedance audio path and high-impedance RF path between the headphone amplifier and the headphone. Ferrite beads should be placed on each antenna conductor connected to nodes other than the FMIP such as left and right audio, microphone audio, switching, etc. In the example shown in Figure 9, these nodes are the left and right audio conductors. Ferrite beads should be 2.5 k $\Omega$  or greater at 100 MHz, such as the Murata BLM18BD252SN1. High resistance at 100 MHz is desirable to maximize R<sub>SHUNT</sub>, and therefore, R<sub>p</sub>. Refer to " Appendix A—FM Receive Headphone Antenna Interface Model" on page 50 for a complete description of R<sub>SHUNT</sub>, R<sub>p</sub>, etc.

ESD diodes D1, D2, and D3 are recommended if design requirements exceed the ESD rating of the headphone amplifier and the Si47xx. Diodes should be chosen with no more than 1 pF parasitic capacitance, such as the California Micro Devices CM1210. Diode capacitance should be minimized to minimize  $C_{SHUNT}$ , and therefore,  $C_P$ . If D1 and D2 must be chosen with a capacitance greater than 1 pF, they should be placed between the ferrite beads F1 and F2 and the headphone amplifier to minimize  $C_{SHUNT}$ . This placement will, however, reduce the effectiveness of the ESD protection devices. Diode D3 may not be relocated and must therefore have a capacitance less than 1 pF. Note that each diode package contains two devices to protect against positive and negative polarity ESD events.

C9 and C10 are 125  $\mu$ F ac coupling capacitors required when the audio amplifier does not have a common mode output voltage and the audio output is swinging above and below ground.

Optional bleed resistors R5 and R6 may be desirable to discharge the ac-coupling capacitors when the headphone cable is removed.

Optional RF shunt capacitors C5 and C6 may be placed on the left and right audio traces at the headphone amplifier output to reduce the level of digital noise passed to the antenna. The recommended value is 100 pF or greater, however, the designer should confirm that the headphone amplifier is capable of driving the selected shunt capacitance.

This schematic example uses the National Semiconductor LM4910 headphone amplifier. Passive components R1– R4 and C7–C8 are required for the LM4910 headphone amplifier as described in the LM4910 data sheet. The gain of the right and left amplifiers is –R3/R1 and –R4/R2, respectively. These gains can be adjusted by changing the values of resistors R3 and R4. As a general guide, gain between 0.6 and 1.0 is recommended for the headphone amplifier, depending on the gain of the headphone elements. Capacitors C7 and C8 are ac-coupling capacitors required for the LM4910 interface. These capacitors, in conjunction with resistors R1 and R2, create a high-pass filter that sets the audio amplifier's lower frequency limit. The high-pass corner frequencies for the right and left amplifiers are:

$$f_{CRIGHT} = \frac{1}{2\pi \cdot R1 \cdot C7}, f_{CLEFT} = \frac{1}{2\pi \cdot R2 \cdot C8}$$

With the specified BOM components, the corner frequency of the headphone amplifier is approximately 20 Hz.

Capacitor C1 is the supply bypass capacitor for the audio amplifier. The LM4910 can also be shut down by applying a logic low voltage to the number 3 pin. The maximum logic low level is 0.4 V and the minimum logic high level is 1.5 V.

The bill of materials for the typical application schematic shown in Figure 6 is provided in Table 12. Note that manufacturer is not critical for resistors and capacitors.

## 3.3. Headphone Antenna Bill of Materials

| Designator     | Description                                                       | Note |

|----------------|-------------------------------------------------------------------|------|

| LMATCH         | IND, 0603, SM, 270 nH, MURATA, LQW18ANR27J00D                     |      |

| C4             | AC coupling cap, SM, 0402, X7R, 100 pF                            |      |

| D1, D2, D3     | IC, SM, ESD DIODE, SOT23-3, California Micro Devices, CM1210-01ST |      |

| U3             | IC, SM, HEADPHONE AMP, National Semiconductor, LM4910MA           |      |

| R1, R2, R3, R4 | RES, SM, 0603, 20 kΩ                                              |      |

| C7, C8         | CAP, SM, 0603, 0.39UF, X7R                                        |      |

| C5, C6         | CAP, SM, 0402, C0G, 100 pF                                        |      |

| R5, R6         | RES, SM, 0603, 100 kΩ                                             |      |

| F1, F2         | FERRITE BEAD, SM, 0603, 2.5 k $\Omega$ , Murata, BLM18BD252SN1D   |      |

| C1             | CAP, SM, 0402, X7R, 0.1 µF                                        |      |

| R7             | RES, SM, 0402, 10 kΩ                                              |      |

<sup>20</sup> Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com Rev. 0.9 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • September 8, 2021

## 3.4. Headphone Antenna Layout

To minimize inductive and capacitive coupling, inductor  $L_{MATCH}$  and headphone jack J24 should be placed together and as far from noise sources such as clocks and digital circuits as possible.  $L_{MATCH}$  should be placed near the headphone connector to keep audio currents away from the Si47xx.

To minimize C<sub>SHUNT</sub> and C<sub>P</sub>, place ferrite beads F1 and F2 as close as possible to the headphone connector.

To maximize ESD protection diode effectiveness, place diodes D1, D2 and D3 as close as possible to the headphone connector. If capacitance larger than 1 pF is required for D1 and D2, both components should be placed between FB1 and FB2 and the headphone amplifier to minimize  $C_{SHUNT}$ .

Place the chip as close as possible to the headphone connector to minimize antenna trace capacitance, CPCBANT. Keep the trace length short and narrow and as far above the reference plane as possible, restrict the trace to a microstrip topology (trace routes on the top or bottom PCB layers only), minimize trace vias, and relieve ground fill on the trace layer. Note that minimizing capacitance has the effect of maximizing characteristic impedance. It is not necessary to design for 50  $\Omega$  transmission lines.

To reduce the level of digital noise passed to the antenna, RF shunt capacitors C5 and C6 may be placed on the left and right audio traces close to the headphone amplifier audio output pins. The recommended value is 100 pF or greater, however, the designer should confirm that the headphone amplifier is capable of driving the selected shunt capacitance.

## 3.5. Headphone Antenna Design Checklist

- □ Select an antenna length of 1.1 to 1.45 m.

- □ Select matching inductor L<sub>MATCH</sub> to maximize signal strength across the FM band.

- □ Select matching inductor L<sub>MATCH</sub> with a Q of 15 or greater at 100 MHz and minimal dc resistance.

- Place inductor L<sub>MATCH</sub> and headphone connector together and as far from potential noise sources as possible to reduce capacitive and inductive coupling.

- □ **Place** the Si47xx close to the headphone connector to minimize antenna trace length. Minimizing trace length reduces CP and the possibility for inductive and capacitive coupling into the antenna by noise sources. This recommendation must be followed for optimal device performance.

- **Select** ferrite beads F1–F2 with 2.5 kΩ or greater resistance at 100 MHz to maximize RSHUNT and, therefore, RP.

- D Place ferrite beads F1-F2 close to the headphone connector.

- □ Select ESD diodes D1-D3 with minimum capacitance.

- □ Place ESD diodes D1-D3 as close as possible to the headphone connector for maximum effectiveness.

- Place optional RF shunt capacitors near the headphone amplifier's left and right audio output pins to reduce the level of digital noise passed to the antenna.

## 4. Cable Antenna for FM Receive on FMI (Si470x/2x/3x/8x Only)

The charger cable of a consumer product can be used as an FM antenna. This section describes how to interface the Si47xx FMI input to a cable antenna.

## 4.1. Cable Antenna Design

Figure 10. Sample Cigarette Lighter Adapter for Cable Antenna

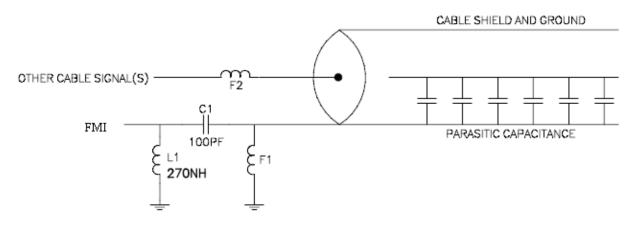

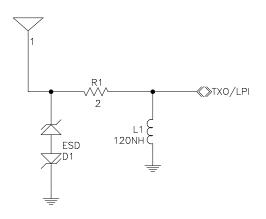

A typical cable antenna contains multiple inner wires/conductors, which are covered with a protective ground shield. The coupling between the wires and the shield can cause the antenna to have large capacitance in the several hundred pico farad range. In order to boost the received FM voltage, it is necessary to minimize this capacitance. This reduction can be achieved by placing ferrite beads in series with each of the antenna's conductors.

## 4.2. Cable Antenna Schematic

Figure 11. Cable Antenna Schematic

To resonate the cable antenna within the FM band, the antenna's capacitance needs to be reduced. As described in Section "4.2. Cable Antenna Schematic", this reduction can be achieved by placing the ferrite beads in series with each of the antenna's conductors. The capacitance should be further controlled by limiting the trace length from the cable ground shield and the RF input pin (FMI input) on the Si47xx FM tuner. Each of the components in the schematic above is explained in detail below:

L1 (27 0nH) is the tuning inductor. This is the typical value used to resonate the cable antenna in the center of the FM band.

F1 (2.5 k $\Omega$  at 100 MHz) is a shunt ferrite to ground at the cable antenna side. A substantial amount of ground return current may flow through the cable antenna shield/ground because there are multiple conductors inside the cable along with power supply conductors. The ferrite will divert the ground return current of the cable antenna to go through the shunt ferrite rather than going through the tuning inductor and/or Si47xx chip.

C1 (100 pF) is a dc blocking cap placed between the FMI pin and the cable antenna ground. The capacitor is used to isolate the cable return currents from the FMI pin.

F2 (2.5 k $\Omega$  at 100 MHz) is a series ferrite placed on the signal conductor in the cable antenna. Note that series ferrites should be placed on each signal conductor in the cable. The ferrite is used to isolate the signal conductors from the shield/ground of the cable antenna and reduce parasitic capacitance seen by the shield/ground. The choice of the ferrite is dependent upon the type of signal on each individual conductor. If the conductor is used to carry power, then a ferrite with a large dc current carrying capability should be used. If the conductor is used to carry high frequency digital signals, make sure that the ferrite does not block the high frequency component of these signals. Likewise if the conductor is used to carry high frequency analog signals, make sure that the ferrite does not filter the high frequency.

## 4.3. Cable Antenna Bill of Materials

The required bill of materials is shown below:

| Designator | Description                                                                                                                                                                                                                                       | Notes                                                                                                                                                                                                              |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L1         | IND, 0603, SM, 270 nH, MURATA,<br>LQW18ANR27J00D                                                                                                                                                                                                  |                                                                                                                                                                                                                    |

| C1         | DC blocking capacitor, SM, 0402, X7R, 100 pF                                                                                                                                                                                                      |                                                                                                                                                                                                                    |

| F1         | Shunt Ferrite bead, FERRITEBEAD, SM, 0603, 470 $\Omega$ , 1 A, Murata, BLM18PG471SN1J                                                                                                                                                             | Rated dc current > max expected<br>ground return current                                                                                                                                                           |

| F2         | Series Ferrite bead, various types.<br>Recommended ferrite for power lines:<br>FERRITEBEAD, SM, 0603, 470 Ω, 1 A, Murata,<br>BLM18PG471SN1J<br>Recommended ferrite for signals: FERRITEBEAD,<br>SM, 0603, 2.5 kΩ, 50 mA Murata,<br>BLM18BD252DN1D | For power signals, make sure the<br>rated dc current > max expected<br>ground return current.<br>For all other signals, make sure<br>ferrite does not block/filter the high<br>frequency component of the signals. |

#### Table 13. Bill of Materials

## 4.4. Cable Antenna Layout

Place the chip as close to the cable antenna as possible. This will minimize the trace length going to the cable antenna which will minimize the parasitic capacitance. Place the shunt ferrite for the ground return current as close to the cable as possible. Putting the shunt ferrite for the ground return current close to the cable ensures that the ground return current has minimal loop which will reduce noise coupling. The series ferrites also should be put as close as possible to the cable. This will minimize the parasitic capacitance seen by the FMI pin.

## 4.5. Cable Antenna Design Checklist

- Place the chip as close as possible to the cable antenna to minimize parasitic capacitance.

- Place the tuning inductor, L1, as far away from noise sources as possible.

- Make sure that the shunt ferrite has a dc rating that exceeds the expected max ground return current of the cable.

- Place the shunt ferrite close to the cable.

- Choose series ferrite that is appropriate for each type of signal in the conductor.

- Place the series ferrite(s) close to the cable.

# 5. Embedded Antenna for FM Transmit on TXO and Receive on LPI (Si4704/05/06/1x/2x Only)

The FM Transmitter component on the Si471x/2x and the FM Receiver component on the Si4704/05/06/2x support an embedded antenna interface through the TXO/LPI pin. In the case of the Si472x FM Transceiver, the same embedded antenna can be used for both FM Transmit and Receive.

## 5.1. Embedded Antenna Design

An embedded antenna can be designed using a loose wire, flex circuit, or PCB trace and can be categorized into two types: stub antenna and loop antenna. For the purpose of this application note, three types of embedded antenna will be covered in detail:

- Embedded stub (wire)

- Embedded loop (wire)

- Embedded stub (PCB trace)

The following table summarizes the advantages and disadvantages of these implementations.

| Antenna                      | Description                                                                                                             | Advantages                                                                                                                                                                        | Disadvantages                                                                                                                                                         |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Embedded Stub (Wire)         | <ul> <li>Wire attached to or<br/>molded inside product<br/>case</li> <li>Connect to pin 4 for<br/>TX/RX</li> </ul>      | <ul> <li>Placement flexibility</li> <li>Minimum PCB space</li> <li>Easy to adjust length<br/>during design testing</li> </ul>                                                     | <ul> <li>Mechanical attachment<br/>to case required</li> <li>Performance can be<br/>impacted by case<br/>shielding</li> </ul>                                         |

| Embedded Loop (Wire)         | <ul> <li>Wire loop attached to or<br/>molded inside product<br/>case</li> <li>Connect to pin 4 for<br/>TX/RX</li> </ul> | <ul> <li>Can achieve high<br/>efficiency per length</li> <li>Placement flexibility</li> <li>Minimum PCB space</li> <li>Easy to adjust length<br/>during design testing</li> </ul> | <ul> <li>Mechanical attachment<br/>to case required</li> <li>Performance can be<br/>impacted by case<br/>shielding</li> </ul>                                         |

| Embedded Stub (PCB<br>Trace) | <ul> <li>Wire trace fabricated on outer PCB copper layer</li> <li>Connect to pin 4 for TX/RX</li> </ul>                 | <ul> <li>No mechanical<br/>attachment to case</li> <li>Ease of product<br/>assembly</li> </ul>                                                                                    | <ul> <li>PCB keep out regions<br/>required around<br/>antenna</li> <li>Additional PCB space</li> <li>Performance can be<br/>impacted by case<br/>shielding</li> </ul> |

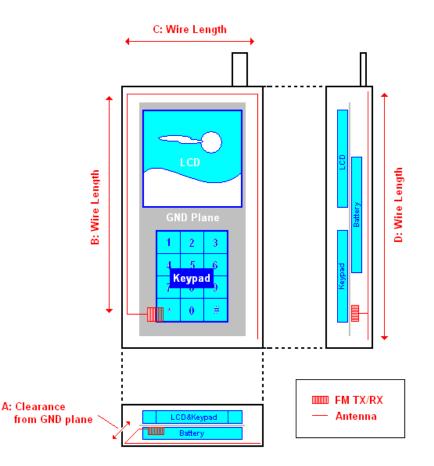

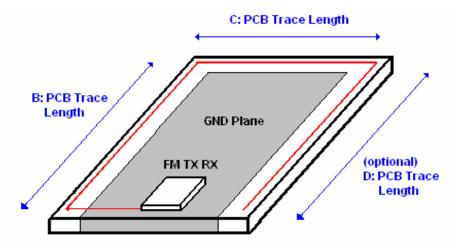

Figure 12 is an example of a stub antenna in wire implementation buried inside a cellular handset. Explanations of the dimensions A, B, C, and D are included later in this document.

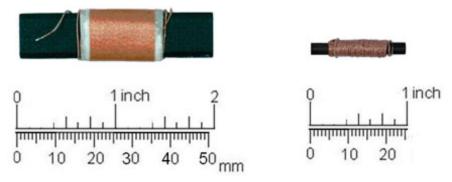

#### 5.1.1. Embedded Stub Antenna—Wire Implementation

A stub (wire) antenna is typically a floating wire that is approximately 10 cm in length and is embedded inside the device with FM functionality. The antenna can be longer if the device's industrial design will accommodate it. The material for a stub (wire) antenna can be an actual wire or a PCB trace. PCB traces can be either in flexible packaging (flexible PCB trace) or as a trace on the PCB. The 24AWG wire has been experimentally proven to have optimal performance.

The stub (wire) antenna should be placed such that it is not obstructed by a ground plane or shield. This requirement can be met by placing the antenna on an extremity of the device (e.g., top or bottom) or on the perimeter. The antenna can also be embedded in the device plastic or outside the plastic with a protective covering. The flexible PCB antenna should be between a PCB and the device plastic such that the antenna trace is not obstructed by a ground plane or shield. The antenna is connected to pin 4 and resonated with the on-chip variable capacitor.

#### 5.1.1.1. Matching

A 10 cm stub (wire) antenna has a capacitive impedance, typically more than 1~2 pF. The antenna is matched by resonating it with a shunt inductor and the on-chip shunt variable capacitor. See Appendix B for inductor value calculation.

#### 5.1.1.2. Configuration

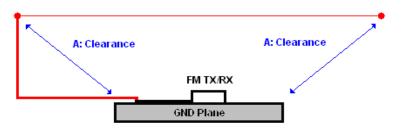

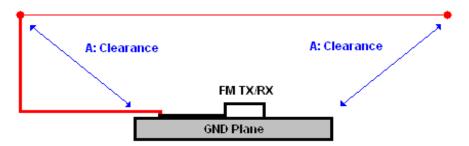

Figure 13. Stub (Wire) Antenna - Side View

Figure 14. U-Shaped Stub (Wire) Antenna—Orthogonal View

## 5.1.1.3. Antenna Layout Guidelines

- Route the antenna as a "U" shape as shown in Figure 14.

- A > 5 mm

- B + C > 10 cm

- Route the antenna as an "L" by removing segment D if a "U" is not possible.

- Maximize antenna length (B+C >10 cm) to provide sufficient radiating power for transmit and maximize incident voltage for receive.

- Keep the antenna as far from the ground plane, shield, and other metal structures (e.g., batteries) as possible (A > 5 mm), and make the enclosure from non-conductive material, such as plastic, to minimize parasitic capacitance and maximize radiation for transmit or maximize incident voltage for receive.

- Antenna capacitance for an ideal wire antenna is approximated by Cant = L/(198 x c), where L is length of wire in meters and c is speed of light (3.0 x 10<sup>8</sup> m/s). A general guideline to follow is to assume that each centimeter of wire antenna adds ~0.17 pF of capacitance (for L << λ/20).</p>

| Length (cm) | C Ant (pF) |

|-------------|------------|

| 10          | 1.68       |

| 11          | 1.85       |

| 12          | 2.02       |

| 13          | 2.19       |

| 14          | 2.36       |

| 15          | 2.53       |

Use an ideal vertical wire antenna as a reference point to measure the performance of the wire antenna. Antenna capacitance will be larger and antenna performance will degrade in a practical application where the wire antenna is bent parallel to the GND plane.

#### 5.1.2. Embedded Loop Antenna—Wire Implementation

A loop (wire) antenna is typically a floating wire that is approximately 13 cm or greater in circumference and is embedded inside the device with FM functionality. It is constructed with a floating wire or flexible PCB trace. The shape of the antenna can be circular or rectangular with the goal of maximizing the enclosed area. The 24AWG has been experimentally proven to have optimal performance. A floating wire antenna is typically embedded in the plastics, or outside of the plastics (with protective covering), at the perimeter of the device such that the antenna trace is not obstructed by the ground plane, shield, or other metal structures (e.g., batteries).

Placement of the flexible PCB is typically between the main PCB and plastics such that the antenna trace is not obstructed by a ground plane or shield. A loop antenna is similar to a short wire antenna with the exception that the other end of the antenna is grounded. Because the other end is grounded, a loop antenna by itself is an inductor.

#### 5.1.2.1. Antenna Matching

A loop (wire) antenna is an inductor of high impedance. The antenna is matched by resonating it with a shunt inductor or capacitor and the on-chip shunt variable capacitor.

#### 5.1.2.2. Configuration

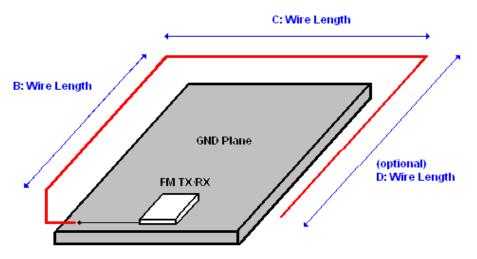

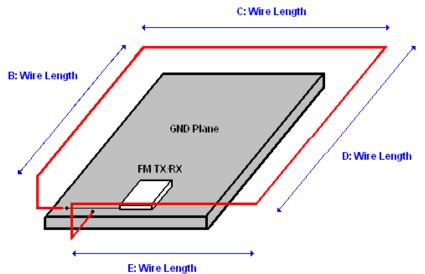

Figure 15. Loop (Wire) Antenna—Side View

Figure 16. Rectangular Loop (Wire) Antenna—Orthogonal View

#### 5.1.2.3. Design Guidelines

- Route the antenna as shown in Figure 16.

- A > 5 mm

- B + C + D + E > 13 cm

- C > 3 cm

- Maximize antenna length (B+C+D+E >13 cm) to provide sufficient radiating power for transmit and maximize incident voltage for receive.

- Keep the antenna as far from the ground plane and shield as possible (A > 5 mm), and make the enclosure from non-conductive material (plastic), to minimize parasitic capacitance and maximize radiation for transmit or maximize incident voltage for receive.

- Antenna inductance for an ideal loop antenna is given by L<sub>ant</sub> = n<sup>2</sup>µ<sub>0</sub>r[ln(8r/b)].

```

r: loop radius (m)

```

n: number of turns

$\mu_0$ : permeability (4 $\pi$  x 10<sup>-7</sup> N/A<sup>2</sup>)

b: wire radius (m)

Number of turns greater than one usually results in a high inductance loop with which the varactor cannot resonate. It is acceptable to place two loops in a parallel structure to reduce the effective inductance.

For a loop with a small radius used in cellular handset or mp3 applications, the loop antenna equation can be approximately applied to a rectangular loop of the same circumference.

| Radius (cm) | Turns | Total Length (cm) | L <sub>ant</sub> (nH) |

|-------------|-------|-------------------|-----------------------|

| 2           | 1     | 12.6              | 111.5                 |

| 3           | 1     | 18.8              | 182.6                 |

| 4           | 1     | 25.1              | 257.9                 |

Use an ideal vertical loop (wire) antenna as a reference point to measure the performance of the loop antenna. Antenna performance will degrade in a practical application where the loop antenna is bent parallel to the GND plane.

#### 5.1.3. Embedded Stub Antenna—PCB Trace Implementation (Pin 4)

A stub antenna (PCB trace) is constructed using a 10 cm or longer PCB trace. The material can be any standard PCB. The PCB trace must be routed in an area without any copper fill, such as ground or power planes or other traces. The antenna is connected to pin 4 and resonated with the on-chip variable capacitor.

Figure 17. Stub (PCB Trace) Antenna—Orthogonal View

#### 5.1.3.1. Antenna Matching

A 10 cm stub (wire) antenna is capacitive, typically more than 1~2 pF. The antenna is matched by resonating it with a shunt inductor and the on-chip shunt variable capacitor. See Appendix A and Appendix B for inductor value calculation.

#### 5.1.3.2. Configuration

Figure 18. Stub (PCB Trace) Antenna—Side View

#### 5.1.3.3. Design Guidelines

- Route the antenna as a "U" shape as shown in Figure 7.

- A > 5 mm

- B + C > 10 cm

- Route the antenna as an "L" by removing segment D if a "U" is not possible.

- Maximize antenna length (B + C >10 cm) to provide sufficient radiating power for transmit and maximize incident voltage for receive.

- It is not important to match D = B.

- Keep the antenna as far from the ground plane and shield as possible (A > 5 mm), and make the enclosure from non-conductive material (plastic), to minimize parasitic capacitance and maximize radiation for transmit or maximize incident voltage for receive.

- Antenna capacitance for an ideal PCB trace antenna is given by Cant = L/(198 x c), where L is length of wire in meters and c is speed of light (3.0 x 10<sup>8</sup> m/s). A general guideline to follow is to assume that each centimeter of wire antenna adds ~0.17 pF of capacitance (for L << λ/20).</p>

| Length (cm) | C <sub>ant</sub> (pF) |

|-------------|-----------------------|

| 10          | 1.68                  |

| 11          | 1.85                  |

| 12          | 2.02                  |

| 13          | 2.19                  |

| 14          | 2.36                  |

| 15          | 2.53                  |

## 5.2. Embedded Antenna Schematic

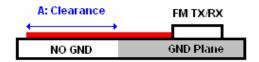

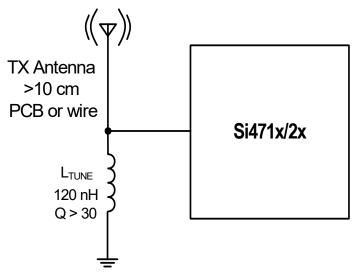

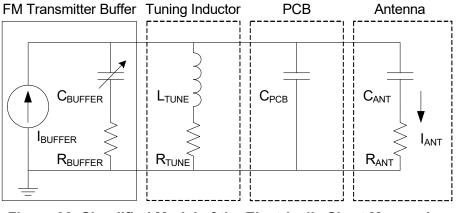

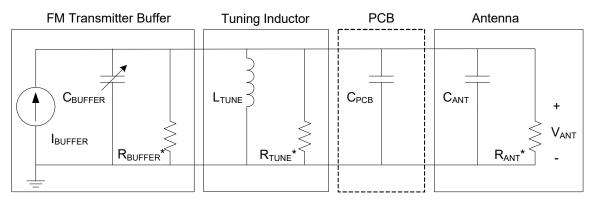

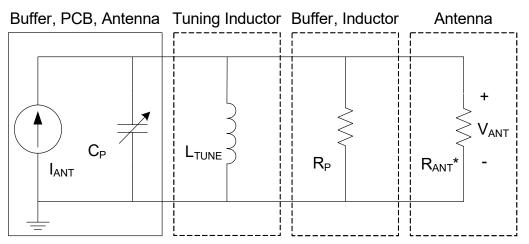

Figure 19 shows the embedded antenna schematic.

#### Figure 19. Embedded Antenna Schematic

L1 is the tuning inductor and typical value is 120nH. L1 needs to be chosen such that the resonant circuit of L1 and the total capacitance at the TXO/LPI pin will resonate at the FM band (76-108MHz). The total capacitance at the TXO/LPI pin includes the internal on-chip varactor, the antenna and all of the parasitic capacitance at that node. Therefore it is important to check the READANTCAP value as described below when the product is in fully assembled configuration.

There are two steps to select the value of L1: calculate L1 using the formula below, and then monitor the on-chip varactor value READANTCAP by sending the TX\_TUNE\_STATUS or FM\_TUNE\_STATUS command to make sure the on-chip varactor is still in-range.

The first step is approximating the value of L1 (which can be skipped). The formula to calculate L1 is as follows:

$$L1 = \frac{1}{(2\pi f)^2 Ctotal}$$

where:

f = frequency of FM band

Ctotal = total capacitance at the TXO/LPI pin

Note that Ctotal will vary because of the automatic tuning of the internal on-chip varactor. The internal on-chip varactor has value from 1-191 for 0.25pF step which equals to 0.25pF to 47.75pF. Knowing the other capacitance at the TXO/LPI pin which is layout and component dependent will give a range of Ctotal. After the approximate Ctotal has been calculated, L1 can be chosen to satisfy the formula above for the FM band.

## AN383

After choosing the right L1 value, the user is still required to check the on-chip varactor value READANTCAP by sending the TX\_TUNE\_STATUS or FM\_TUNE\_STATUS command to make sure that the on-chip varactor has not gone out-of-range. User also can jump to this second step right away and skip the first step of approximating L1 by trying different values of L1.

The procedure to monitor the READANTCAP is as follows:

- Select at least three frequencies in the bottom, middle and top of the FM band (e.g. 88, 98, and 108 MHz) and get the READANTCAP values.

- It is even better if user sweeps the entire FM band and gets the READANTCAP values.

- L1 has a correct inductance value if

- 1 < READANTCAP < 191

- READANTCAP at 88 MHz > READANTCAP at 98 MHz > READANTCAP at 108 MHz

- Be suspicious when READANTCAP returns the middle value of 97. It may be an indication that the inductor value is not correct.

- L1 is not the right value and needs to be changed if either one of these three conditions occur:

- READANTCAP returns the bottom value of 1: it indicates that there is too much capacitance at the TXO/LPI pin. L1 needs to be adjusted to a smaller value or the better solution is to try to reduce the parasitic capacitance at the TXO/LPI pin

- READANTCAP returns a middle value of 97: it indicates that there is way too much capacitance at the TXO/LPI pin. L1 needs to be adjusted to a smaller value or the better solution is to try to reduce the parasitic capacitance at the TXO/LPI pin pin

- READANTCAP returns the top value of 191: it indicates that there is too little of a capacitance at the TXO/LPI pin (unlikely to happen). L1 needs to be adjusted to a bigger value.

The rest of the components in the embedded antenna schematic are optional.

D1 is the ESD diode and it is only necessary when there is an exposed pad going to the TXO/LPI pin.

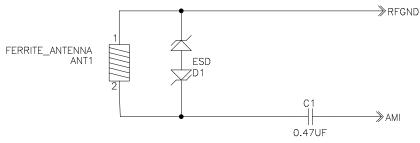

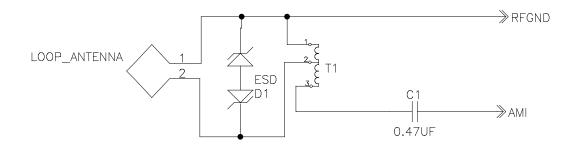

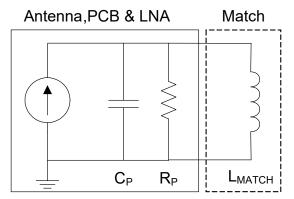

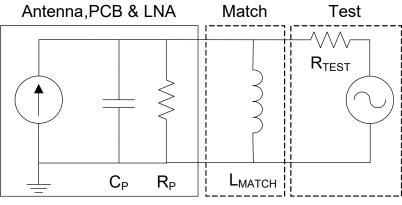

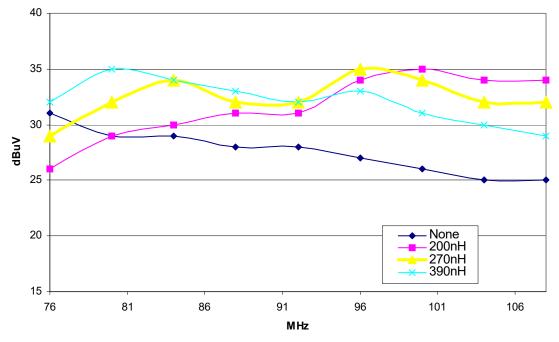

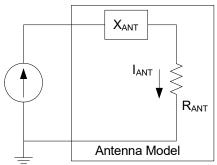

R1 is the ESD current limiting resistor and used in conjunction with D1. It is only necessary when there is an exposed pad going to the TXO/LPI pin.